Computer science department

# **Electronics**

Author: A.prof Ahmed Magdy DR Dina Awny

## Electronics

### **ACKNOWLEDGEMENTS**

First before anything I will thank great God (Allah) who gives us the ability to finish this work.

Second, We are extremely grateful to our parents who have sacrificed themselves to give us the best education. From our early childhood, they raised us to love learning, and every one whose supported us to develop our interest in science and engineering. Their unreserved love and support for these many years is what makes this possible. I would also like to thank them for their continuous support, for their patience, encouragement and extra care.

Thank you all.

### **ABSTRACT**

The course description of this course can be summarized and classified to two main branches as the following:

- ➤ Electrical part: Basic concepts: SI Units, SI prefixes, charge, current, voltage, power, energy, active elements, and passive elements. Basic laws: ohm's law, conductance, Node, branch, node, Kirchhoff's current law (KCL), Kirchhoff's voltage law (KVL), Series resistance, voltage division, Parallel resistance, and current division. Electrical circuit analysis method and Circuit theorem: Nodal analysis (elimination technique, Cramer's rule, Super node and inspection method for nodal analysis), mesh analysis (Cramer's rule and inspection method for mesh analysis), Superposition, Source transformation, Thevenin's theorem, Norton theorem and Maximum power transfer. Inductors, Capacitors and Transient circuits: Inductors, Capacitors, First order transient circuit (Source free R-C circuit, Forced R-C circuit, Source free R-L circuit and Forced R-L circuit) and Second order transient circuit (R-L-C circuit). Sinusoidal steady state analysis: Phasors and sin wave, Electrical circuit analysis, Circuit theorems and Average and RMS.

- ➤ Electronic part: Semiconductors and diode: Material types and properties of semiconductors, Doping process, N-type and P-type, P-N junction, Models for diode and Diode applications (HWR and FWR). Bipolar Junction Transistor (BJT): Basics and fundamentals, Biasing. Field Effect Transistor (FET): Basics and fundamentals, Classification, Biasing. Finally operational Amplifier (OPAMP): Basics and fundamentals, properties of OPAMP and OPAMP applications.

### TABLE OF CONTENTS

| ABSTRACT                          |                                      | III  |

|-----------------------------------|--------------------------------------|------|

| TABLE OF CONTENTS LIST OF FIGURES |                                      | IV   |

|                                   |                                      | VIII |

| LIST OF TABL                      | ES                                   | XIII |

| LIST OF SYMB                      | BOLS                                 | XIV  |

| ACRONYMS                          |                                      | XV   |

| CHAPTER 1:                        | CIRCUIT VARIABLES AND ELEMENTS       |      |

| 1.1.Basic concept                 | ts                                   | 2    |

| 1.1.1                             | The international system of units    | 2    |

| 1.1.2                             | The international system of prefixes | 2    |

| 1.2.Circuit variab                | bles                                 | 3    |

| 1.2.1                             | Electrical charge                    | 3    |

| 1.2.2                             | Electrical current                   | 3    |

| 1.2.3                             | Voltage                              | 4    |

| 1.2.4                             | Power                                | 4    |

| 1.2.5                             | Energy                               | 5    |

| 1.3.Circuit eleme                 | ents                                 | 5    |

| 1.3.1                             | Passive elements                     | 6    |

| 1.3.2                             | Active elements                      | 7    |

| 1.4.Basic laws an                 | nd definitions                       | 7    |

| 1.4.1                             | Ohm's law and conductance            | 7    |

| 1.4.2                             | Node, loop and branch                | 9    |

| <b>1.5.</b> Sheet 1               |                                      | 10   |

|                                   |                                      |      |

| <b>CHA</b>  | <u>PTER 2</u> : T | ECHNIQUES OF CIRCUIT A  | NALYSIS                |

|-------------|-------------------|-------------------------|------------------------|

| 2.1         | Kirchhoff's       | current and voltage law | 15                     |

| 2.2         | Series and p      | arallel resistance      | 17                     |

| 2.3         | Voltage and       | current division        | 19                     |

| 2.4         | Nodal analy       | sis                     | 20                     |

| 2.5         | Mesh analys       | sis                     | 22                     |

| 2.6         | Superposition     | on                      | 24                     |

| 2.7         | Thevenin's th     | neorem                  | 25                     |

| 2.8         | Norton theo       | rem                     | 26                     |

| 2.9         | Source trans      | sformation              | 27                     |

| 2.10        | Sheet 2           |                         | 29                     |

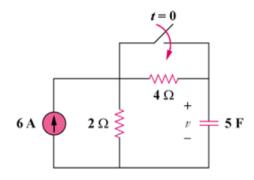

| CHA<br>CIRO |                   | NATURAL AND STEP RESPON | NSE FOR RL, RC AND RLC |

| 3.1         | Inductors         |                         | 35                     |

| 3.2         | Capacitors        |                         | 36                     |

| 3.3         | First order to    | ransient circuit        | 37                     |

|             | 3.3.1             | Source free R-C circuit | 38                     |

|             | 3.3.2             | Forced R-C circuit      | 40                     |

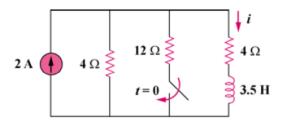

|             | 3.3.3             | Source free R-L circuit | 41                     |

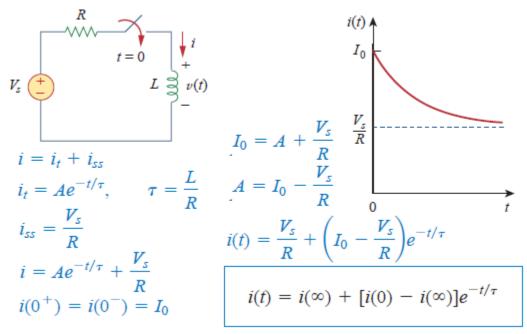

|             | 3.3.4             | Forced R-L circuit      | 43                     |

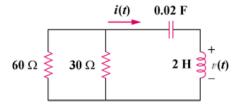

| 3.4         | Second orde       | er transient circuit    | 44                     |

| 3.5         | Sheet 3           |                         | 47                     |

| <u>CHA</u>  | <u>PTER 4</u> : S | INUSOIDAL STEADY STATE  | ANALYSIS               |

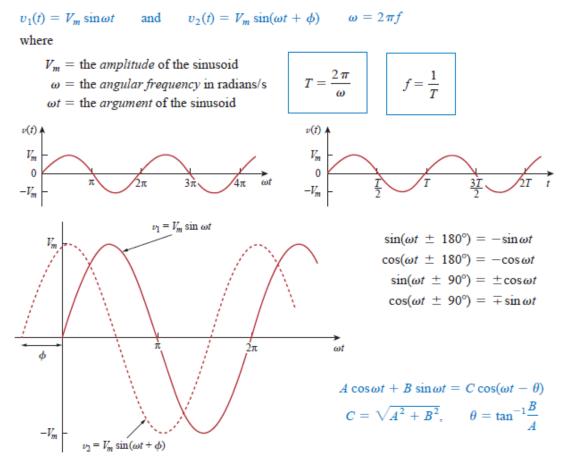

| 4.1         | Phasors and       | sin wave                | 50                     |

| 4.2       | Electrical circuit analysis. |                                           | 51 |

|-----------|------------------------------|-------------------------------------------|----|

| 4.3       | Average and RMS              |                                           | 52 |

| 4.4       | Sheet 4                      |                                           | 53 |

| <u>CH</u> | <u> APTER 5</u> : I          | INTRODUCTION OF SEMICONDUCTORS            |    |

| 5.1       | Fundamenta                   | als of atoms                              | 57 |

|           | 5.1.1                        | Definitions of atom                       | 57 |

|           | 5.1.2                        | Atomic number and Atomic weight           | 57 |

|           | 5.1.3                        | Orbits and shells                         | 58 |

| 5.2       | Basic of ma                  | aterials                                  | 58 |

|           | 5.2.1                        | Resistivity                               | 58 |

|           | 5.2.2                        | Insulators, semiconductors and conductors | 58 |

| 5.3       | Semiconduc                   | ctor concepts                             | 59 |

|           | 5.3.1                        | Doping process                            | 60 |

|           | 5.3.2                        | N-type material                           | 60 |

|           | 5.3.3                        | P-type material                           | 60 |

|           | 5.3.4                        | Depletion layer                           | 61 |

|           | 5.3.5                        | Barrier potential                         | 61 |

|           | 5.3.6                        | Forward bias and reverse bias             | 62 |

|           | 5.3.7                        | Electronic and hole currents              | 62 |

| 5.4       | Sheet 5                      |                                           | 63 |

| <u>CH</u> | <u> APTER 6</u> : I          | DIODE AND ITS APPLICATIONS                |    |

| 6.1       | Introduction                 | n of diode                                | 65 |

| 6.2       | models of d                  | liode                                     | 65 |

|           | 6.2.1                        | ideal model                               | 65 |

| 6.2.2                   | Barrier constant model                 | 66       |

|-------------------------|----------------------------------------|----------|

| 6.2.3                   | Linear model                           | 66       |

| 6.2.4                   | Actual model                           | 66       |

| <b>6.3</b> Applicat     | tions of diode                         | 67       |

| 6.3.1                   | DC applications of diode               | 67       |

| 6.3.2                   | AC applications of diode               | 68       |

| <b>6.4</b> Sheet 6      |                                        | 73       |

| CHAPTER 7               | 7: Different Types of Transistor       |          |

| <b>7.1</b> Basics of Bi | polar Junction Transistor (BJT)        | 75       |

| <b>7.</b> 1             | <b>1.1</b> BJT definition              | 76       |

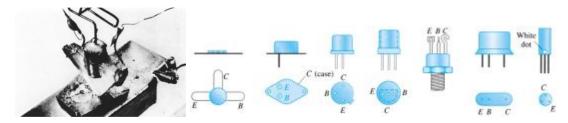

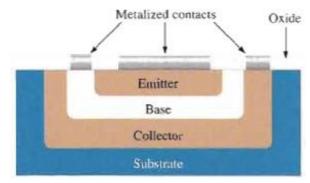

| <b>7.</b> 1             | 1.2 BJT construction, model and symbol | 76       |

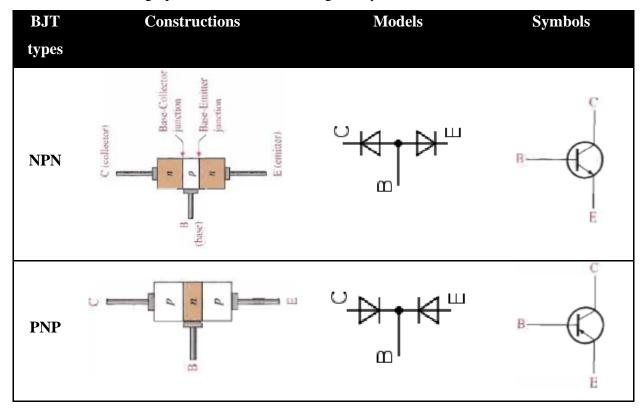

| <b>7.</b> 1             | <b>1.3</b> BJT operations              | 77<br>78 |

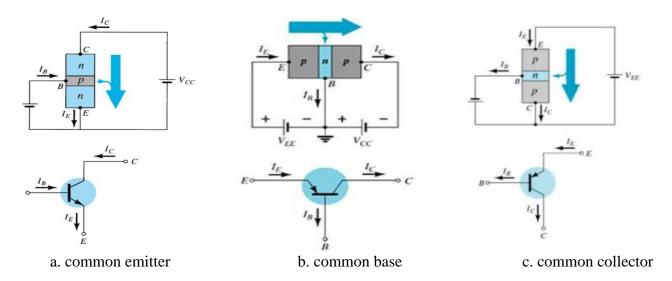

| <b>7.</b> 1             | 1.4 BJT configurations                 | 79       |

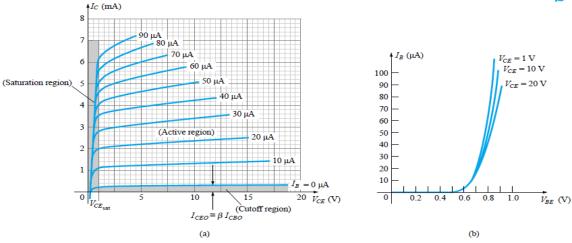

| <b>7.</b> 1             | 1.5 BJT characteristics curves         | 81       |

| <b>7.</b> 1             | <b>1.6</b> DC biasing                  | 82       |

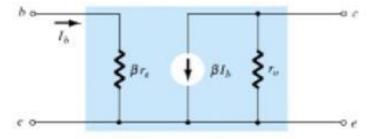

| <b>7.</b> 1             | 1.7 AC analysis for BJT                | 82       |

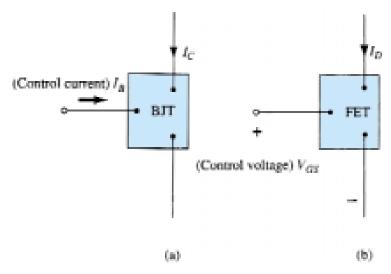

| 7.2Basics of I          | Field Effect Transistors (FET)         | 80       |

| 7.2                     | 2.1 FET overview                       | 80       |

| 7.2                     | 2.2 FET definition                     | 81       |

| 7.2                     | 2.3 FET properties                     | 81       |

| 7.3FET classi           | ification                              | 86       |

| <b>7.3.1</b> JFET                        | 89  |

|------------------------------------------|-----|

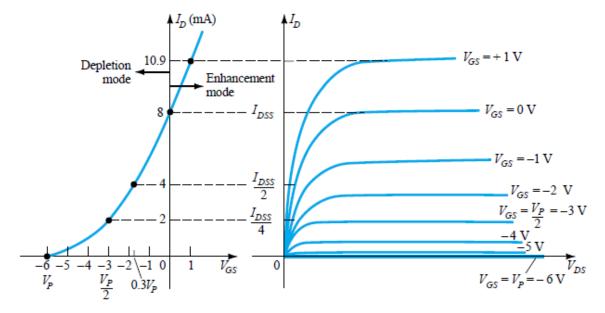

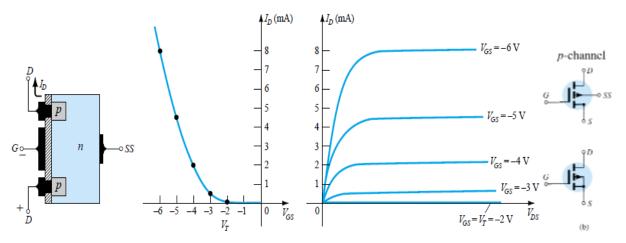

| <b>7.3.2</b> Depletion MOSFET            | 95  |

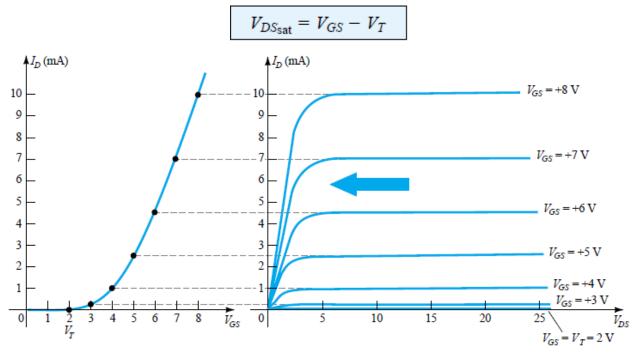

| <b>7.3.3</b> Enhancement MOSFET          | 97  |

| <b>7.4</b> DC analysis for FET           | 98  |

| <b>7.5</b> AC analysis for FET           | 99  |

| <b>7.6</b> Sheet 7                       | 107 |

| CHAPTER 8: Operational Amplifier (OPAMP) |     |

| 8.1 Introduction                         | 103 |

| <b>8.2</b> Properties of OPAMP           | 105 |

| <b>8.3</b> OPAMP applications            | 103 |

| <b>8.4</b> Sheet 8                       | 113 |

| REFERENCES                               | 115 |

### LIST OF FIGURES

| Fig. 1.1:  | DC and AC electric current.                               | 4  |

|------------|-----------------------------------------------------------|----|

| Fig. 1.2:  | The difference between power absorbed and power supplied. | 5  |

| Fig. 1.3:  | circuit elements.                                         | 6  |

| Fig. 1.4:  | Resistor and its circuit.                                 | 7  |

| Fig. 1.5:  | Short circuit and open circuit.                           | 8  |

| Fig. 1.6:  | Branch, Node and Loop.                                    | 9  |

| Fig. 2.1:  | Example on KCL.                                           | 15 |

| Fig. 2.2:  | Another example on KCL.                                   | 15 |

| Fig. 2.3:  | Example on KVL.                                           | 16 |

| Fig. 2.4:  | A single-loop circuit with two resistors in series.       | 17 |

| Fig. 2.5:  | A single-loop circuit with two resistors in parallel.     | 18 |

| Fig. 2.6:  | Symbols of references node.                               | 20 |

| Fig. 2.7:  | Typical circuit for nodal analysis.                       | 21 |

| Fig. 2.8:  | Nodal analysis with voltage source.                       | 22 |

| Fig. 2.9:  | Typical circuit for mesh analysis.                        | 23 |

| Fig. 2.10: | Mesh analysis with current source.                        | 24 |

| Fig. 2.11: | Superposition circuits.                                   | 25 |

| Fig. 2.12: | Thevenin's circuits.                                      | 25 |

| Fig. 2.13: | Norton circuits.                                          | 26 |

| Fig. 2.14: | Source transformation circuits.                           | 27 |

| Fig. 2.15: | Source transformation example.                            | 28 |

| Fig. 3.1:  | Inductors.                                                | 35 |

| Fig. 3.2:  | Capacitors.                                               | 36 |

| Fig. 3.3:  | Comparison between capacitors, inductors and resistors.                | 37 |

|------------|------------------------------------------------------------------------|----|

| Fig. 3.4:  | Meaning of transient.                                                  | 37 |

| Fig. 3.5:  | Source free R-C circuit.                                               | 38 |

| Fig. 3.6:  | Forced R-C circuit.                                                    | 41 |

| Fig. 3.7:  | Source free R-L circuit.                                               | 42 |

| Fig. 3.8:  | Forced R-L circuit                                                     | 44 |

| Fig. 3.9:  | Source free R-L-C circuit.                                             | 45 |

| Fig. 3.10: | Three types of RLC circuit cases.                                      | 46 |

| Fig. 4.1:  | Sinusoidal wave properties.                                            | 1  |

| Fig. 4.2:  | Phasor properties.                                                     | 1  |

| Fig. 4.3:  | Phasor relationships of circuit elements.                              | 1  |

| Fig. 4.4:  | Example on circuit analysis with R, L and C.                           | 1  |

| Fig. 5.1:  | Bohr model for atomic structure.                                       | 1  |

| Fig. 5.2:  | Energy diagram for (a)Insulators, (b)Semiconductors and (c)conductors. | 1  |

| Fig. 5.3:  | Intrinsic semiconductor.                                               | 1  |

| Fig. 5.4:  | N-type material.                                                       | 1  |

| Fig. 5.5:  | P-type material.                                                       | 1  |

| Fig. 5.6:  | PN junction.                                                           | 1  |

| Fig. 5.7:  | Diode biasing.                                                         | 1  |

| Fig. 6.1:  | Characteristics curve for Si diode.                                    | 1  |

| Fig. 6.2:  | Ideal model.                                                           | 1  |

| Fig. 6.3:  | Barrier potential (constant) model.                                    | 1  |

| Fig. 6.4:  | Linear (piecewise) model.                                              | 1  |

| Fig. 6.5:  | Actual (Practical) model.                                              | 1  |

| Fig. 6.6:  | Example 6.1.                                                           | 1  |

| Fig. 6.7:  | HWR circuit                                                            | 1  |

|            |                                                                        |    |

| Fig. 6.8:  | Center-tapped circuit.                                                                                                                   | 1  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 6.9:  | Bridge circuit.                                                                                                                          | 1  |

| Fig. 7.1:  | The first transistor and others                                                                                                          | 76 |

| Fig. 7.2:  | The BJT structure planar                                                                                                                 | 76 |

| Fig. 7.3:  | The BJT as amplifier                                                                                                                     | 78 |

| Fig 7.4    | BJT configurations                                                                                                                       | 79 |

| Fig. 7.5:  | The Characteristics of a silicon transistor in the common-emitter configuration:(a) collector characteristics; (b) base characteristics. | 79 |

| Fig 7.6    | re model for BJT                                                                                                                         | 82 |

| Fig. 7.7:  | (a) BJT and (b) FET                                                                                                                      | 83 |

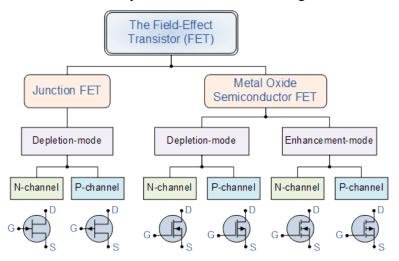

| Fig. 7.8:  | Classification of FETs.                                                                                                                  | 84 |

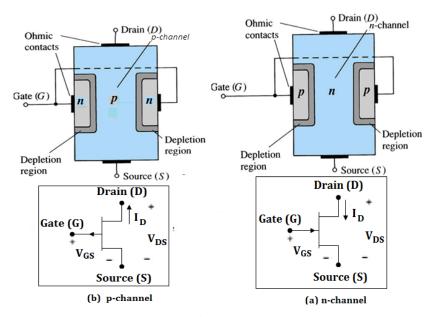

| Fig. 7.9:  | JFETs.                                                                                                                                   | 85 |

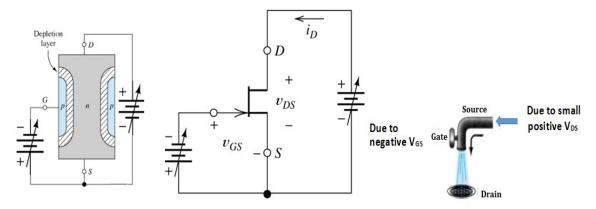

| Fig. 7.10: | N channel JFET.                                                                                                                          | 86 |

| Fig. 7.11: | The effect $V_{GS}$ .                                                                                                                    | 86 |

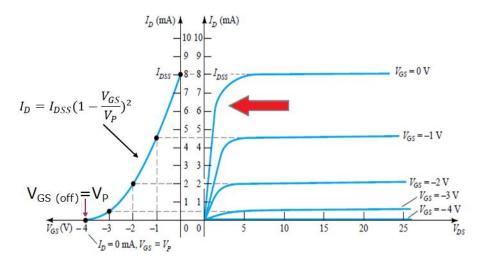

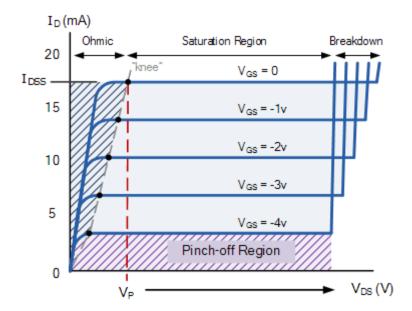

| Fig. 7.12: | The transfer characteristics curve for JFET.                                                                                             | 88 |

| Fig. 7.13: | The characteristics curves for JFET.                                                                                                     | 89 |

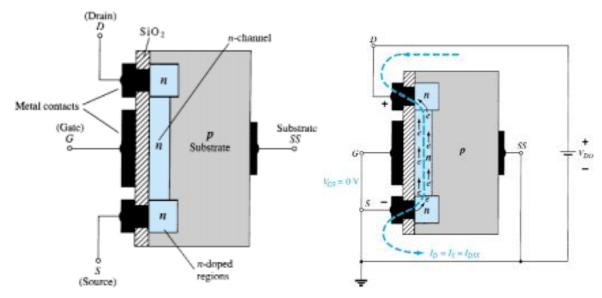

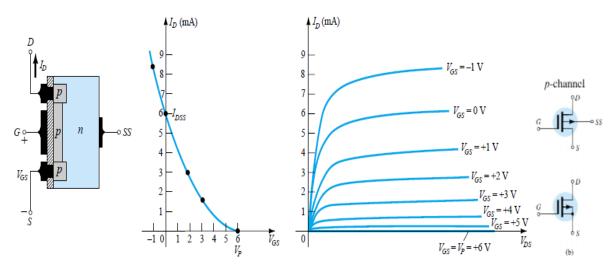

| Fig. 7.14: | The <i>n</i> -Channel depletion-type MOSFET.                                                                                             | 90 |

| Fig. 7.15: | The Drain and transfer characteristics for an n-channel depletion-type MOSFET.                                                           | 91 |

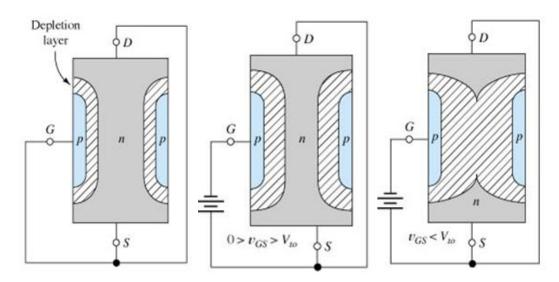

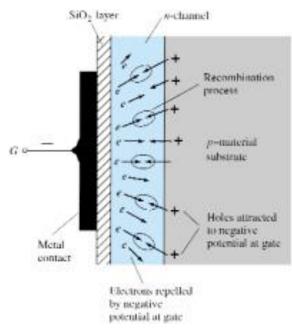

| Fig. 7.16: | Reduction in free carriers in channel due to a negative potential at the gate terminal.                                                  | 92 |

| Fig. 7.17: | P-channel depletion MOSFET                                                                                                               | 93 |

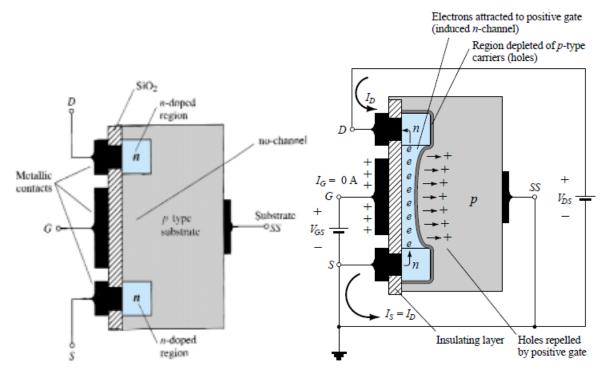

| Fig. 7.18: | The <i>n</i> -Channel enhancement type MOSFET.                                                                                           | 94 |

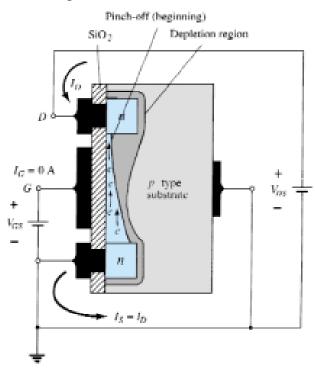

| Fig. 7.19: | Change in channel and depletion region                       | 95  |

|------------|--------------------------------------------------------------|-----|

| Fig. 7.20: | The characteristics for an n-channel enhancement type MOSFET | 96  |

| Fig. 7.21: | P-channel enhancement MOSFET                                 | 97  |

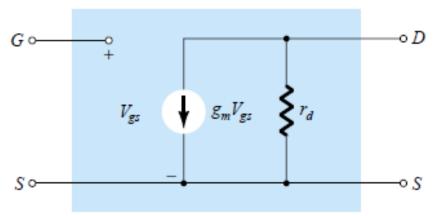

| Fig 7.22:  | FET AC equivalent circuit                                    | 100 |

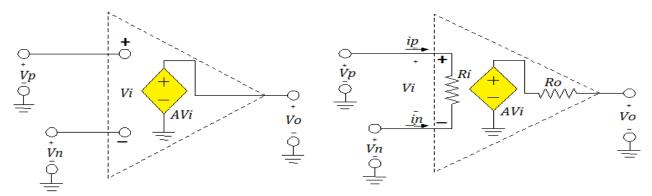

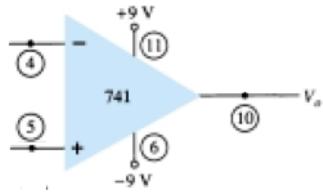

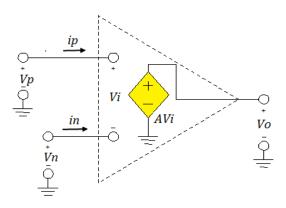

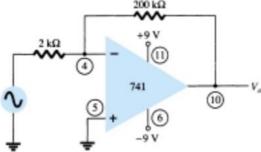

| Fig. 8.1:  | Ideal and standard OPAMP.                                    | 103 |

| Fig. 8.2:  | Terminals of OPAMP.                                          | 104 |

| Fig. 8.3:  | Characteristics of Ideal OPAMP.                              | 105 |

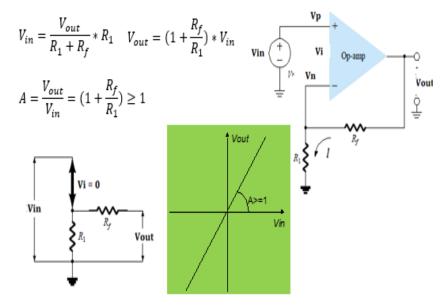

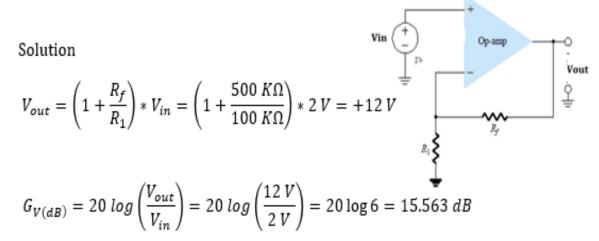

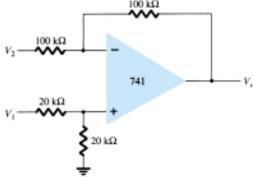

| Fig. 8.4:  | Non-Inverting Amplifier                                      | 105 |

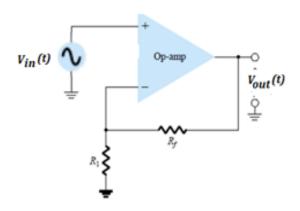

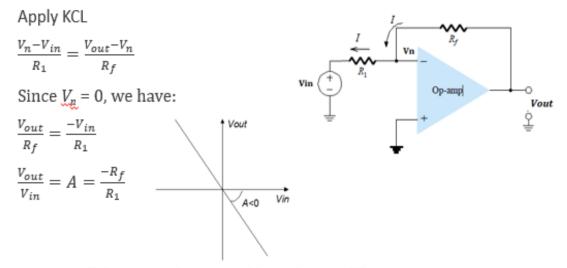

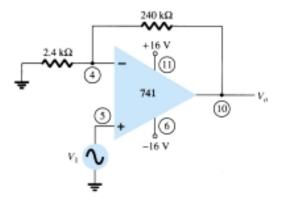

| Fig. 8.5:  | Inverting Amplifier                                          | 106 |

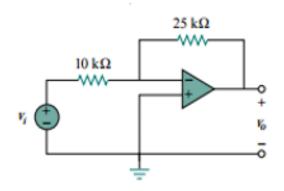

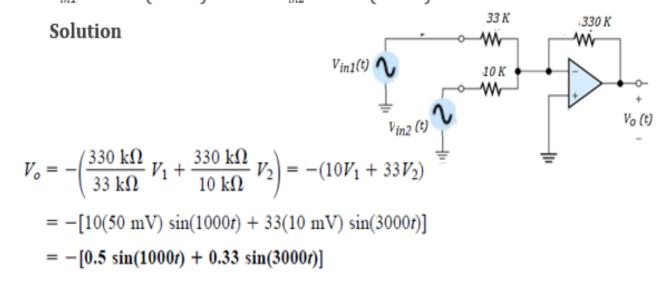

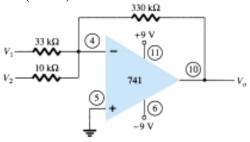

| Fig. 8.6:  | Summing Amplifier                                            | 108 |

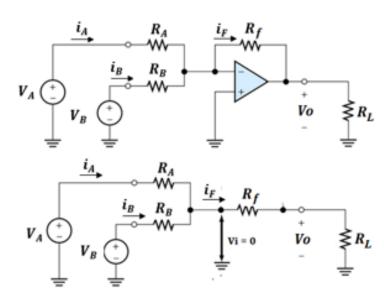

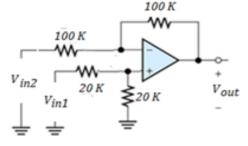

| Fig. 8.7:  | Subtractor Amplifier                                         | 109 |

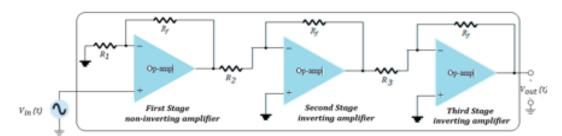

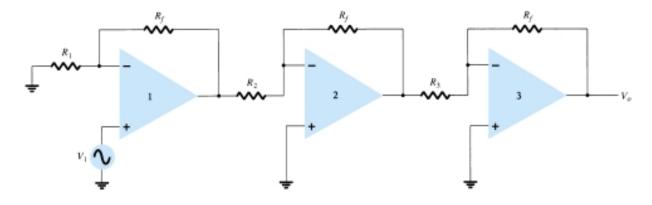

| Fig. 8.8:  | Multiple-Stage                                               | 110 |

### LIST OF TABLES

| Table 1.1: | SI units.                                        | 1  |

|------------|--------------------------------------------------|----|

| Table 1.2: | SI prefixes.                                     | 1  |

| Table 1.3: | Some of material resistivity.                    | 1  |

| Table 7.1  | The BJT graph construction, modeling and symbols | 76 |

| Table 7.2: | The BJT modes                                    | 79 |

| Table 7.3  | The BJT configurations.                          | 79 |

| Table 7.4  | DC biasing circuits                              | 81 |

### LIST OF SYMBOLS

Ampere A C Capacitance D Diode Е Energy I Electrical current Imaginary J L Inductance P Power R Resistance V Volt 3 Permittivity Mobility μ Partial differentiation δ Angle

φ

### ACRONYMS

Avg Average

F.B Forward Bias

FWR Full Wave Rectifier

HWR Half Wave Rectifier

KCL Kirchhoff's Current Law

KVL Kirchhoff's Voltage Law

RMS Root Mean Square

R.B Reverse Bias

### **CHAPTER 1**

### **CIRCUIT VARIABLES AND ELEMENTS**

#### **CHAPTER 1**

#### CIRCUIT VARIABLES AND ELEMENTS

#### 1.1. Basic concepts

The electrical engineering is one of the most important field. First, we need to understand the basic concepts for electrical circuits.

#### **1.1.1** The international system of units

Here in this subsection, we will state the standard international (SI) units in electrical part in this course as shown in table 1.1.

Table 1.1. SI units

| Quantity                  | Basic unit | Symbol |

|---------------------------|------------|--------|

| Time                      | Second     | S      |

| Length                    | Meter      | M      |

| Electric current          | Ampere     | A      |

| Thermodynamic temperature | Kelvin     | K      |

#### **1.1.2** The international system of prefixes

As shown in the following table 1.2, the international system of prefixes will be illustrated.

**Example 1.1:** estimate the following values in V and A.

$V_1 = 10 \text{ KV} = 10 * 1000 = 10000 \text{ V}.$

$V_2 = 10 \text{ mV} = 10/1000 = 0.01 \text{ V}.$

$I_1 = 20 \text{ mA} = 20/1000 = 0.02 \text{ A}.$

$I_2 = 300 \text{ nA} = 30*10^{-9} = 0.0000003 \text{ A}.$

$V_3 = 1 \text{ MV} = 1 * 10^6 = 1000000 \text{ V}.$

Table 1.2. SI prefixes

| Multiplier        | Prefix | Symbol |

|-------------------|--------|--------|

| 10 <sup>18</sup>  | exa    | E      |

| 10 <sup>15</sup>  | peta   | P      |

| 10 <sup>12</sup>  | tera   | T      |

| 10 <sup>9</sup>   | giga   | G      |

| 10 <sup>6</sup>   | mega   | M      |

| 10 <sup>3</sup>   | kilo   | K      |

| 10 <sup>2</sup>   | hecto  | Н      |

| 10 <sup>1</sup>   | deka   | Da     |

| 10 <sup>-1</sup>  | deci   | D      |

| 10 <sup>-2</sup>  | centi  | С      |

| 10 <sup>-3</sup>  | milli  | M      |

| 10 <sup>-6</sup>  | micro  | μ      |

| 10 <sup>-9</sup>  | nano   | N      |

| 10 <sup>-12</sup> | pico   | P      |

| 10 <sup>-15</sup> | femto  | F      |

| 10 <sup>-18</sup> | atto   | A      |

#### 1.2. Circuit variables

#### 1.2.1 Electrical charge

The definition of the electrical charge, is an electrical property of the atomic particles of which matter consists, measured in coulombs (C). Its symbols are Q or q(t).

#### 1.2.2 Electrical current

The definition of the electrical current, is the time rate of change of charge, measured in amperes (A). Its symbols are I or i(t). In addition to the relation between electric current and charge is illustrated as the following:

$$i = \frac{dq}{dt}$$

and  $q = \int_{t_0}^{t} i \, dt$  where 1 A= 1 C/s

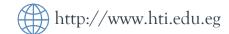

As shown in figure 1.1, we found two types in electric current. The first one is DC current which is a current that remains constant with time. The second one is AC current which is a current that varies sinusoidal with time.

Fig. 1.1: DC and AC electric current

#### 1.2.3 Voltage

The definition of the electrical voltage difference between two points is the energy or work needed to move unit charge from first point to second point, measured in volts (V). Its symbols are V or v(t). In addition to the relation between electric voltage and charge is illustrated as the following:

$$v = \frac{dw}{dq}$$

where 1 V= 1 J/C.

#### **1.2.4** Power

The definition of the power, is the time rate of expending and absorbing energy, measured in watts (W). Its symbols are P or p(t). In addition to the relation between power and energy is illustrated as the following:

$$p = \frac{dw}{dt} = \frac{dw}{dq} * \frac{dq}{dt} = v * i \text{ where } 1 \text{ W} = 1 \text{ J/s}.$$

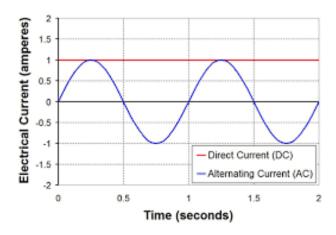

When the current enters through the positive terminal of an element the relation is p = +vi but if enters through the negative terminal of an element the relation is p = -vi (power absorbed = - power supplied) as shown in figure 1.2.

Fig. 1.2: The difference between power absorbed and power supplied

#### **1.2.5** Energy

The definition of the energy, is the capacity to do work, measured in joules (J). Its symbols are W or w(t). In addition to the relation between power and energy is illustrated as the following:

$$w = \int_{t_0}^t p \, dt = \int_{t_0}^t v * i \, dt$$

**Example 1.2:** Calculate the energy were consumed in three hours when 200 W electric bulb

$$w = p*t = 200 * 2 * 3600 = 1440 \text{ kJ}$$

is the same  $w = p * t = 200*2 = 400 \text{ Wh}$ .

#### 1.3. Circuit elements

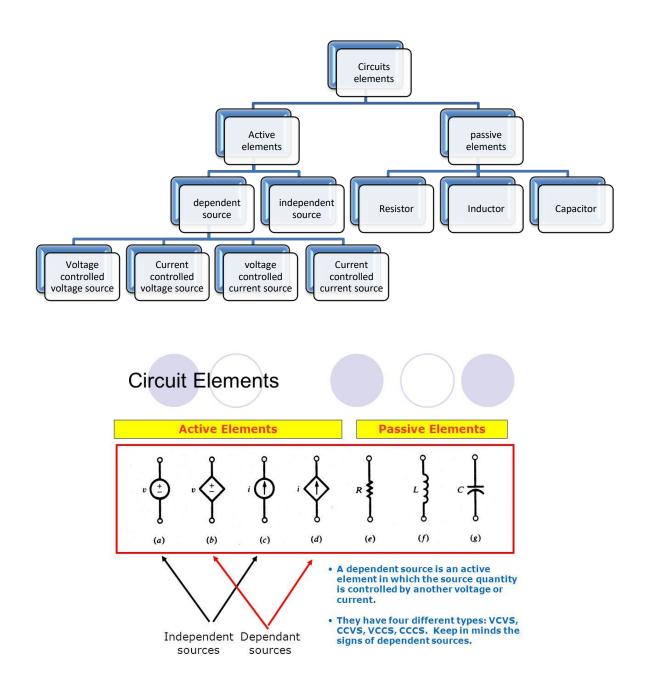

Circuit elements are the main parts in any electrical circuits and are classified into two types as the following subsections and figure 1.3:

Fig. 1.3: circuit elements

#### **1.3.1** Passive elements

Many components are considered as passive element such as resistor, capacitors, inductors and etc...

#### 1.3.2 Active elements

Many components are considered as active element such as voltage and current source. We can state the four important dependent type:

- voltage controlled voltage source

- > current controlled voltage source

- > current controlled current source

- voltage controlled current source

#### 1.4. Basic laws and definitions

#### 1.4.1 Ohm's law and conductance

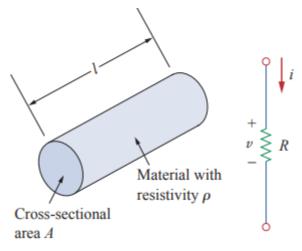

Ohm's law states that the voltage v across a resistor is directly proportional to the current i flowing through the resistor. That is mean v  $\alpha$  i where v = i \* R. Where the resistance of an element denotes its ability to resist the flow of electrical current, it is measured on ohms  $(\Omega)$ . Where the resistance of any material with a uniform cross-sectional area A depends on A and its length , as shown in figure 1.4. We can represent resistance as measured in the laboratory, in mathematical form  $R = \rho L/A$ ,

Fig. 1.4: Resistor and its circuit

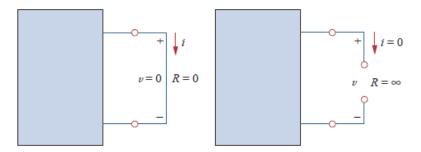

where  $\rho$  is known as the resistivity of the material in ohm-meters. Good conductors, such as copper and aluminum, have low resistivity, while insulators, such as mica and paper, have high resistivity. Table 1.3 presents the values of for some common materials and shows which materials are used for conductors, insulators, and semiconductors. We have special cases asshown in figure 1.5, when an open circuit is

found that is mean  $R=\infty$  and when an short circuit is found that is mean R=0. On the other hand, conductance is the ability of an element to conduct electrical current, it is measured by moh ( $\sigma$ ) or Siemens (S) and G=i\*v. Now we can say  $p=vi=i^2R=v^2/R=v^2G=i^2/G$ .

**Table 1.3.** Some of material resistivity

| Materials | Resistivity | Usage         |

|-----------|-------------|---------------|

| Copper    | 1.72*10-8   | Conductor     |

| Teflon    | 3*1012      | Insulators    |

| Silicon   | 6.4*102     | Semiconductor |

| Germanium | 47*10-2     | Semiconductor |

Fig. 1.5: Short circuit and open circuit

**Example 1.3:** The essential component of a toaster is an electrical element (a resistor) that converts electrical energy to heat energy. How much current is drawn by a toaster with resistance  $10 \Omega$  at 110 V?

Answer: 11 A.

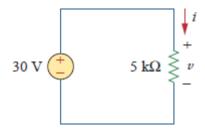

**Example 1.4:** In the circuit shown in the following figure, calculate the current i, the conductance G, and the power p.

#### **Answer:**

$i = v/R = 30/5*10^3 = 6 \text{ mA}$ G = i/v = 1/R = 0.2 mS

P = v\*i = 180 mW

#### 1.4.2 Node, loop and branch

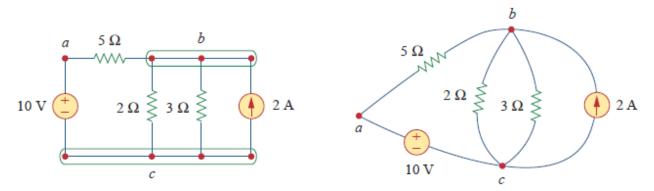

As shown in the figure 1.6, we will present some definitions:

- ➤ Branch: represents a single element such as a voltage source or a resistor.

- Node: is a point to connect between two or more branches.

- ➤ Loop: is any closed path in the electrical circuit.

Fig. 1.6: Branch, Node and Loop

**Example 1.5:** Determine the number of branches and nodes in the circuit shown in the following figures. Identify which elements are in series and which are in parallel.

#### Answer:

(a) Since there are four elements in the circuit, the circuit has four branches: 10 V, 5  $\Omega$ ,  $6\Omega$ , and 2 A. The circuit has three nodes as identified in Fig. (a). The  $5\Omega$  resistor is in series with the 10-V voltage source because the same current would flow in both. The 6-resistor is in parallel with the 2-A current source because both are connected to the same nodes 2 and 3.

(b) Five branches and three nodes are identified in Fig. (b). The  $1\Omega$  and  $2\Omega$  resistors are in parallel. The  $4\Omega$  resistor and 10-V source are also in parallel.

#### 1.5. Sheet 1

1. Determine the current flowing through an element if the charge flow is given by:

(a)

$$q(t) = (3t + 8) \text{ mC}$$

(b)  $q(t) = (8t^2 + 4t - 2) \text{ C}$

(c)  $q(t) = (3e^{-t} - 5e^{-2t}) \text{ nC}$

(d)  $q(t) = 10 \sin 120 \pi t \text{ pC}$

(e)  $q(t) = 20e^{-4t} \cos 50t \mu\text{C}$

2. Find the charge flowing through a device if the current is:

(a)

$$i(t) = 3 \text{ A}, q(0) = 1 \text{ C}$$

(b)  $i(t) = (2t + 5) \text{ mA}, q(0) = 0$

(c)  $i(t) = 20 \cos(10t + \pi/6)\mu\text{A}, q(0) = 2 \mu\text{C}$

(d)  $i(t) = 10e^{-30t} \sin 40t \text{ A}, q(0) = 0$

- 3. A rechargeable flashlight battery is capable of delivering 85 mA for about 12 h. How much charge can it release at that rate? If its terminal voltage is 1.2 V, how much energy can the battery deliver?

- 4. If the current flowing through an element is given by

$$i(t) = \begin{cases} 3tA, & 0 & \le t < 6 \text{ s} \\ 18A, & 6 & \le t < 10 \text{ s} \\ -12A, & 10 & \le t < 15 \text{ s} \\ 0, & t \ge 15 \text{ s} \end{cases}$$

Plot the charge stored in the element over 0 < t < 20 s.

- 5. The current entering the positive terminal of a device is  $i(t) = 3 e^{-2t} A$  and the voltage across the device is  $v(t) = 5 \operatorname{di/dt} V$ .

- (a) Find the charge delivered to the device between t = 0 and t = 2 s.

- (b) Calculate the power absorbed.

- (c) Determine the energy absorbed in 3 s.

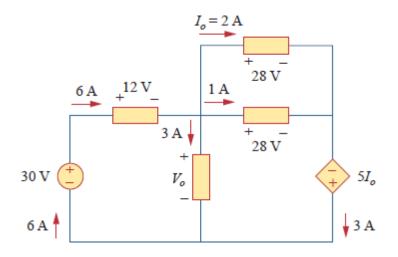

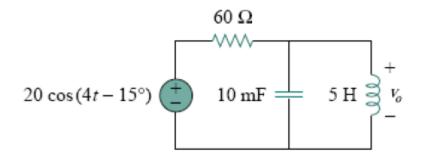

- 6. Find V<sub>0</sub> in the circuit of the following figure

7. An electric stove with four burners and an oven is used in preparing a meal as follows.

Burner 1: 20 minutes Burner 2: 40 minutes Burner 3: 15 minutes Burner 4: 45 minutes

Oven: 30 minutes

If each burner is rated at 1.2 kW and the oven at 1.8 kW, and electricity costs 12 cents per kWh, calculate the cost of electricity used in preparing the meal.

- 8. Find the power rating of the following electrical appliances in your household:

- (a) Light bulb

- (b) Radio set

- (c) TV set

- (d) Refrigerator

- (e) Personal computer

- (f) PC printer

- (g) Microwave oven

- (h) Blender

- 9. A 1.5-kW electric heater is connected to a 120-V source.

- (a) How much current does the heater draw?

- (b) If the heater is on for 45 minutes, how much energy is consumed in kilowatthours (kWh)?

- (c) Calculate the cost of operating the heater for 45 minutes if energy costs 10 cents/kWh.

- 10. A flashlight battery has a rating of 0.8 ampere-hours (Ah) and a lifetime of 10 hours.

- (a) How much current can it deliver?

- (b) How much power can it give if its terminal voltage is 6 V?

- (c) How much energy is stored in the battery in kWh?

- 11. GPU Energy (the electric power company in New Jersey) charged a consumer \$52.75 one month. If the basic service charge is \$5.23 and the company charges \$0.11 per kWh, how much energy in kWh was used by the consumer?

- 12. How much energy does a 10-hp motor deliver in 30 minutes? Assume that 1 horse power = 746 W.

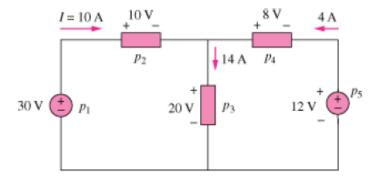

- 13. Find the power absorbed by each of the elements in the following figure:

- 14. The voltage across a 5-k $\Omega$  resistor is 16 V. Find the current through the resistor.

- 15. Find the hot resistance of a lightbulb rated 60 W, 120 V.

- 16. When the voltage across a resistor is 120 V, the current through it is 2.5 mA. Calculate its conductance.

- (a) Calculate current i in the following figure when the switch is in position 1.

- (b) Find the current when the switch is in position 2.

### **CHAPTER 2**

### TECHNIQUES OF CIRCUIT ANALYSIS

#### **CHAPTER 2**

#### TECHNIQUES OF CIRCUIT ANALYSIS

#### 2.1 Kirchhoff's current and voltage law

In Kirchhoff's current law (KCL) states that the algebraic sum of currents entering a node (or a closed boundary) is zero. Mathematically, KCL implies that

$$\sum_{n=1}^{N} i_n = 0$$

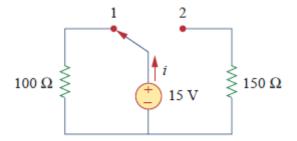

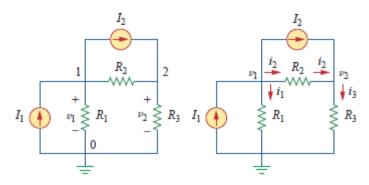

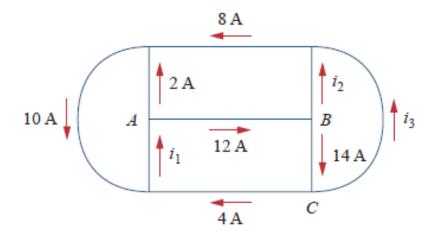

where N is the number of branches connected to the node and  $i_n$  is the n-th current entering (or leaving) the node. As shown in figure 2.1, by this law, currents entering a node may be regarded as positive, while currents leaving the node may be taken as negative or vice versa.

Fig. 2.1: Example on KCL

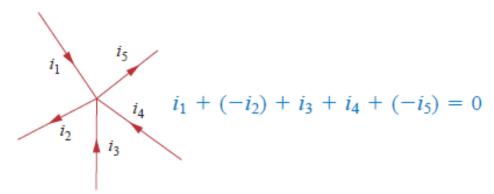

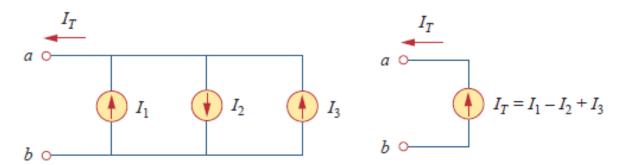

As shown in figure 2.2, the sum of the currents entering a node is equal to the sum of the currents leaving the node.

Fig. 2.2: Another example on KCL

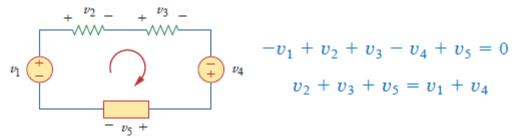

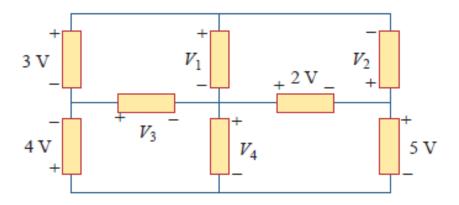

In Kirchhoff's voltage law (KVL) states that the algebraic sum of all voltages around a closed path (or loop) is zero. Mathematically, KVL implies that

$$\sum_{m=1}^{M} v_m = 0$$

where M is the number of voltages in the loop (or the number of branches in the loop) and  $v_m$  is the m-th voltage. As shown in figure 2.3, by this law, The sign on each voltage is the polarity of the terminal encountered first as we travel around the loop. We can start with any branch and go around the loop either clockwise or counterclockwise. In other words, sum of voltage drops = sum of voltage rises

Fig. 2.3: Example on KVL

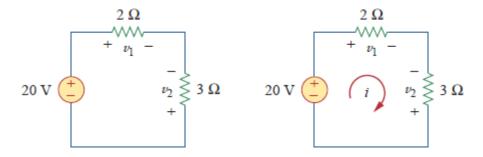

**Example 2.1:** For the circuit in the following figure, find voltages  $v_1$  and  $v_2$ .

Answer: To find  $v_1$  and  $v_2$  we apply Ohm's law and Kirchhoff's voltage law. Assume that current i flows through the loop as shown in Fig.. From Ohm's law,

$$v_1=2i$$

,  $v_2=-3i$ .

Applying KVL around the loop gives

$$-20 + v_1 - v_2 = 0$$

we obtain i = 4 A.

$$v_1 = 8 \text{ V} \text{ and } v_2 = -12 \text{ V}$$

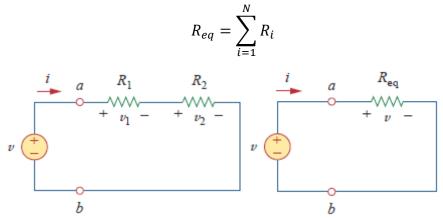

#### 2.2 Series and parallel resistance

The process of combining the resistors is facilitated by combining two of them at a time. With this in mind, consider the single-loop circuit of figure 2.4. The two resistors are in series, since the same current i flows in both of them. Applying Ohm's law to each of the resistors, we obtain

$$v_1 = i R_1 \text{ and } v_2 = i R_2$$

$-v + v_1 + v_2 = 0$

$v = v_1 + v_2 = i(R_1 + R_2)$

$i = \frac{v}{(R_1 + R_2)}$

$v = i R_{eq}$

$R_{eq} = R_1 + R_2$

Now we can say The equivalent resistance of any number of resistors connected in series is the sum of the individual resistances.

Fig. 2.4: A single-loop circuit with two resistors in series.

If

$$R_1 = R_2 = \cdots = R_N = R$$

, then

$$R_{ea} = NR$$

where two resistors are connected in parallel and therefore have the same voltage across them as shown in figure 2.5. From Ohm's law,

$$v = iR_1 = iR_2$$

$$i_1 = \frac{v}{R_1}, \qquad i_2 = \frac{v}{R_2}$$

$$i = i_1 + i_2 = \frac{v}{R_1} + \frac{v}{R_2} = v\left(\frac{1}{R_1} + \frac{1}{R_2}\right) = \frac{v}{R_{eq}}$$

$$\frac{1}{R_{eq}} = \frac{1}{R_1} + \frac{1}{R_2}$$

$$R_{eq} = \frac{R_1 R_2}{R_1 + R_2}$$

$$\frac{1}{R_{eq}} = \frac{1}{R_1} + \frac{1}{R_2} + \dots + \frac{1}{R_N}$$

The equivalent resistance of two parallel resistors is equal to the product of their resistances divided by their sum.

Fig. 2.5: A single-loop circuit with two resistors in parallel.

Note that the equivalent resistance is always smaller than the resistance of the smallest resistor in the parallel combination. If  $R_1 = R_2 = \cdots = R_N = R$ , then

$$R_{eq} = \frac{R}{N}$$

The equivalent conductance of resistors connected in parallel is the sum of their individual conductance.

$$G_{eq} = G_1 + G_2 + \dots + G_N$$

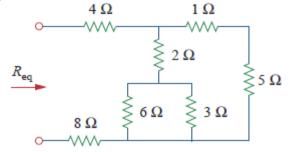

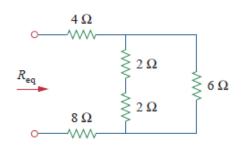

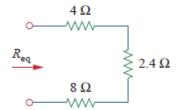

**Example 2.2:** Find  $R_{eq}$  for the circuit shown in the following figure

#### **Answer:**

Two resistors 6 and 3 parallel

$$6 // 3 = 2 \Omega$$

Two resistors 2 and 2 series and parallel with 6

$$(2+2) // 6 = 2.4 \Omega$$

Three resistances 4, 8 and 2.4 are series

$$4 + 8 + 2.4 = 14.4 \Omega$$

**Example 2.3:** Find  $R_{eq}$  for the circuit shown in the following figure

Answer: 6 Ω.

#### 2.3 Voltage and current division

To determine the voltage across each resistor by using voltage divider in figure 2.4 as the following

$$v_{1} = \frac{R_{1}}{(R_{1} + R_{2})} v \qquad v_{2} = \frac{R_{2}}{(R_{1} + R_{2})} v$$

$$v_{i} = \frac{R_{i}}{(R_{1} + R_{2} + \dots + R_{N})} v$$

To determine the current through each resistor by using current divider in figure 2.5 as the following

$$v = iR_{eq} = \frac{iR_1R_2}{(R_1 + R_2)} = i_1R_1 = i_2R_2$$

$$i_1 = \frac{R_2}{(R_1 + R_2)}i$$

$$i_2 = \frac{R_1}{(R_1 + R_2)}i$$

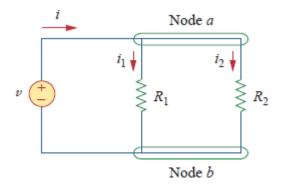

#### 2.4 Nodal analysis

Nodal analysis provides a general procedure for analyzing circuits using node voltages as the circuit variables. Choosing node voltages instead of element voltages as circuit variables is convenient and reduces the number of equations one must solve simultaneously. To simplify matters, we shall assume in this section that circuits do not contain voltage sources. Circuits that contain voltage sources will be analyzed in the next section. In nodal analysis, we are interested in finding the node voltages. Given a circuit with n nodes without voltage sources, the nodal analysis of the circuit involves taking the following three steps.

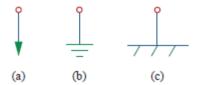

- Select a node as the reference node as shown in figure 2.6. Assign voltages  $v_1, v_2, ..., v_n$  to the remaining (n-1) nodes. The voltages are referenced with respect to the reference node.

- ➤ Apply KCL to each of the (n-1) non-reference nodes. Use Ohm's law to express the branch currents in terms of node voltages.

- > Solve the resulting simultaneous equations to obtain the unknown node voltages.

**Fig. 2.6:** Symbols of references node.

As shown in figure 2.7, Current flows from a higher potential to a lower potential in a resistor.

$$i = \frac{v_{higher} - v_{lower}}{R}$$

$$i_1 = \frac{v_1 - 0}{R_1} = G_1 v_1$$

$$i_2 = \frac{v_1 - v_2}{R_2} = G_2 (v_1 - v_2)$$

$$i_3 = \frac{v_2 - 0}{R_3} = G_3 v_2$$

$$I_1 = I_2 + \frac{v_1}{R_1} + \frac{v_1 - v_2}{R_2}$$

node 2:

$$\frac{v_2}{R_3} = I_2 + \frac{v_1 - v_2}{R_2}$$

Fig. 2.7: Typical circuit for nodal analysis.

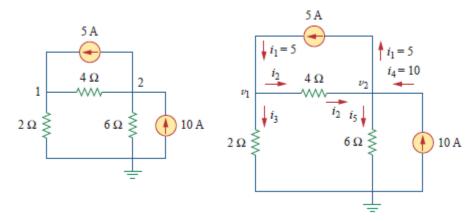

#### **Example 2.4:** Find $v_1$ and $v_2$ using nodal analysis:

Answer: At node 1, applying KCL and Ohm's law gives

node 1:

$$i_1 = i_2 + i_3$$

$$5 = \frac{v_1 - v_2}{4} + \frac{v_1 - 0}{2} \tag{1}$$

node 2:

$$i_2 + i_4 = i_1 + i_5$$

$$\frac{v_1 - v_2}{4} + 10 = 5 + \frac{v_2 - 0}{6}$$

(2)

from (1) and (2)

$$v_1 = 13.33V$$

and  $v_2 = 20V$ .

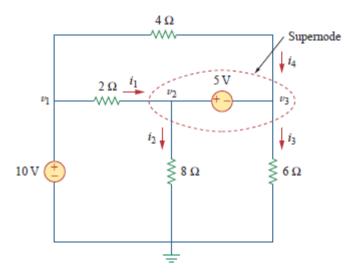

Nodal analysis with voltage source is called super-node (A super-node is formed by enclosing a (dependent or independent) voltage source connected between two non-reference nodes and any elements connected in parallel with it.) and considers as special case.

➤ CASE 1 If a voltage source is connected between the reference node and a non-reference node, we simply set the voltage at the non-reference node equal to the voltage of the voltage source. In figure 2.8., for example,

$$v_1 = 10V$$

Thus, our analysis is somewhat simplified by this knowledge of the voltage at this node.

➤ CASE 2 If the voltage source (dependent or independent) is connected between two non-reference nodes, the two non-reference nodes form a generalized node or super-node; we apply both KCL and KVL to determine the node voltages. We can solve the following three equation to find all three voltages.

$$i_{1} + i_{4} = i_{2} + i_{3}$$

$$\frac{v_{1} - v_{2}}{2} + \frac{v_{1} - v_{3}}{4} = \frac{v_{2} - 0}{8} + \frac{v_{3} - 0}{6}$$

(1)

$$v_{2} - v_{3} = 5$$

(2)

$$v_{1} = 10$$

(3)

Fig. 2.8: Nodal analysis with voltage source

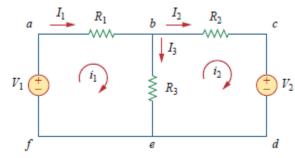

#### 2.5 Mesh analysis

In the mesh analysis of a circuit with n meshes, we take the following three steps.

- Assign mesh currents  $i_1, i_2, ..., i_n$  to the n meshes.

- > Apply KVL to each of the n meshes. Use Ohm's law to express the voltages in terms of the mesh currents.

- > Solve the resulting n simultaneous equations to get the mesh currents.

As shown in figure 2.9, loop 1:

$$-V_1 + R_1 i_1 + R_3 (i_1 - i_2) = 0$$

loop 2:

$$R_2 i_2 + V_2 + R_3 (i_2 - i_1) = 0$$

After we will solve the two equation we can find:

$$I_1 = i_1$$

,  $I_2 = i_2$  and  $I_3 = i_1 - i_2$

Fig. 2.9: Typical circuit for mesh analysis.

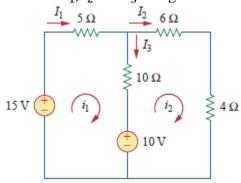

**Example 2.5:** Find the branch currents  $I_1$ ,  $I_2$  and  $I_3$  using mesh analysis.

Answer: We first obtain the mesh currents using KVL. For mesh 1,

$$-15 + 5i_1 + 10(i_1 - i_2) + 10 = 0$$

(1)

and for mesh 2

$$6i_2 + 4i_2 + 10(i_2 - i_1) - 10 = 0$$

(2)

from (1) and (2)

$$i_1 = i_2 = 1A$$

$I_1 = i_1 = 1A$ ,  $I_2 = i_2 = 1A$  and  $I_3 = i_1 - i_2 = 0A$

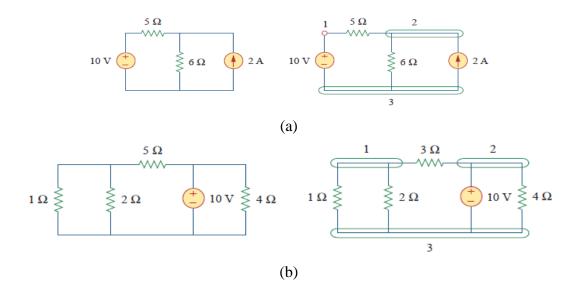

Mesh Analysis with Current Sources is called super-mesh (A super-mesh results when two meshes have a (dependent or independent) current source in common..) and considers as special case.

➤ CASE 1 When a current source exists only in one mesh: Consider the circuit in figure 2.10(c), for example. We set  $i_2 = -5$  A and write a mesh equation for the other mesh in the usual way; that is,

$$v_1 = 10V$$

Thus, our analysis is somewhat simplified by this knowledge of the voltage at this node.

➤ CASE 2 When a current source exists between two meshes: Consider the circuit in figure 2.10(a), for example. We create a super-mesh by excluding the current source and any elements connected in series with it, as shown in figure 2.10(b).

Fig. 2.10: Mesh analysis with current source

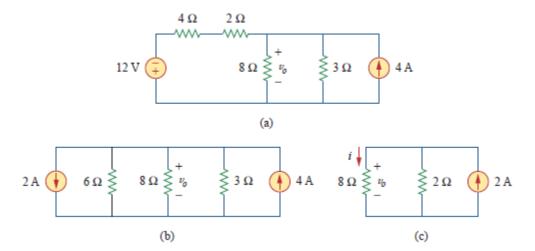

#### 2.6 Superposition

The superposition principle states that the voltage across (or current through) an element in a linear circuit is the algebraic sum of the voltages across (or currents through) that element due to each independent source acting alone. With these in mind, we apply the superposition principle in three steps:

- > Turn off all independent sources except one source. Find the output (voltage or current) due to that active source using the techniques covered in this chapter.

- Repeat step 1 for each of the other independent sources.

- Find the total contribution by adding algebraically all the contributions due to the independent sources.

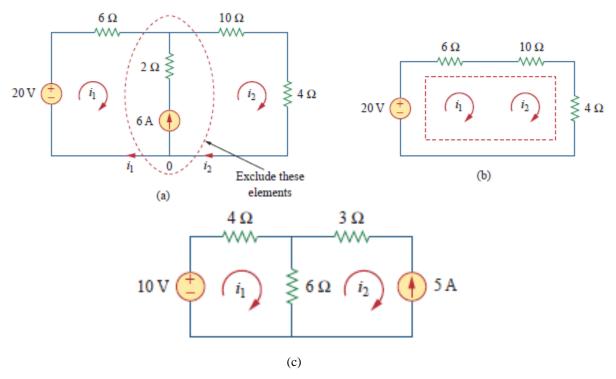

**Example 2.6:** Use the superposition theorem to find v in the circuit of figure 2.11.

**Answer:**

$$v = v_1 + v_2$$

from figure 2.11a by voltage divider

$$v_1 = 4i_1 = \frac{4}{4+8} * 6 = 2V$$

from figure 2.11b by current divider

$$v_2 = 4i_3 = 4 * \frac{8}{4+8} * 3 = 8V$$

$$v = v_1 + v_2 = 2 + 8 = 10V$$

Fig. 2.11: Superposition circuits

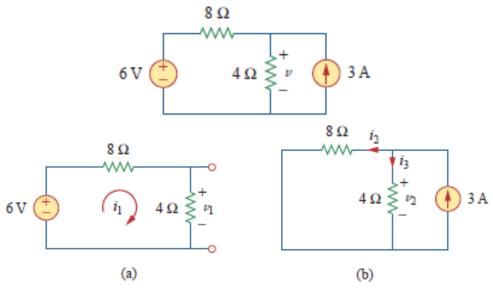

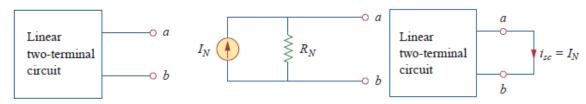

#### 2.7 Thevenin's theorem

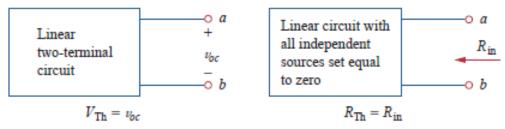

Thevenin's theorem states that a linear two-terminal circuit can be replaced by an equivalent circuit consisting of a voltage source  $V_{Th}$  in series with a resistor  $R_{Th}$ , where  $V_{Th}$  is the open-circuit voltage at the terminals and  $R_{Th}$  is the input or equivalent resistance at the terminals when the independent sources are turned off as shown in figure 2.12.

Fig. 2.12: Thevenin's circuits

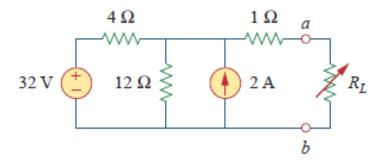

**Example 2.7:** Find the Thevenin equivalent circuit of the circuit shown, to the left of the terminals a - b.

**Answer:**

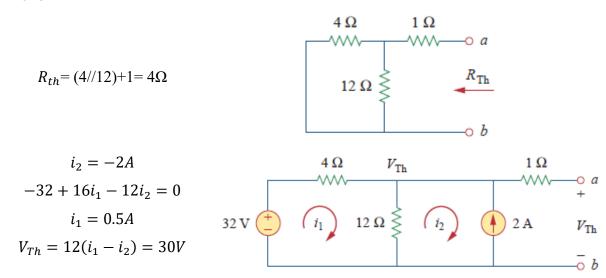

#### 2.8 Norton theorem

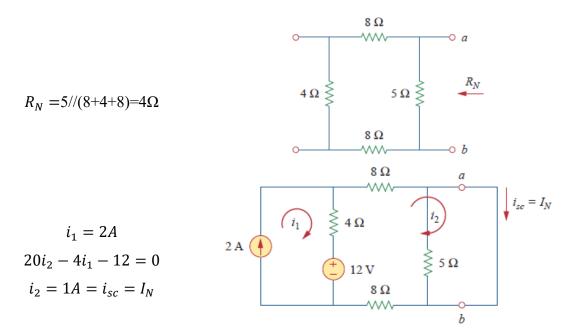

Norton's theorem states that a linear two-terminal circuit can be replaced by an equivalent circuit consisting of a current source  $I_N = V_{Th}/R_{Th}$  in parallel with a resistor  $R_N = R_{Th}$ , where  $I_N$  is the short-circuit current through the terminals and  $R_N$  is the input or equivalent resistance at the terminals when the independent sources are turned off.

Fig. 2.13: Norton circuits

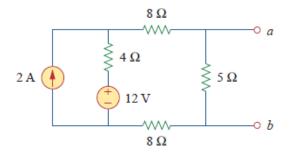

**Example 2.8:** Find the Norton equivalent circuit of the circuit shown, to the left of the terminals a - b.

**Answer:**

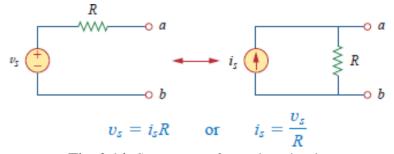

#### 2.9 Source transformation

A source transformation is the process of replacing a voltage source  $v_s$  in series with a resistor R by a current source is in parallel with a resistor R, or vice versa as shown in figure 2.14.

Fig. 2.14: Source transformation circuits

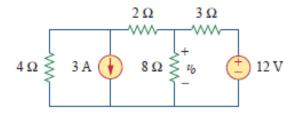

**Example 2.9:** Use source transformation to find  $v_0$  in the following circuit.

Answer: We first transform the current and voltage sources to obtain the circuit in figure 2.15(a). Combining the  $4\Omega$  and  $2\Omega$  resistors in series and transforming the 12-V voltage source gives us figure 2.15(b). We now combine the  $3\Omega$  and  $6\Omega$  resistors in parallel to get  $2\Omega$ . We also combine the 2-A and 4-A current sources to get a 2-A source. Thus, by repeatedly applying source transformations, we obtain the circuit in figure 2.15(c).

$$v_0 = 8i = 8 * \frac{2}{2+8} * 2 = 3.2V$$

Fig. 2.15: Source transformation example

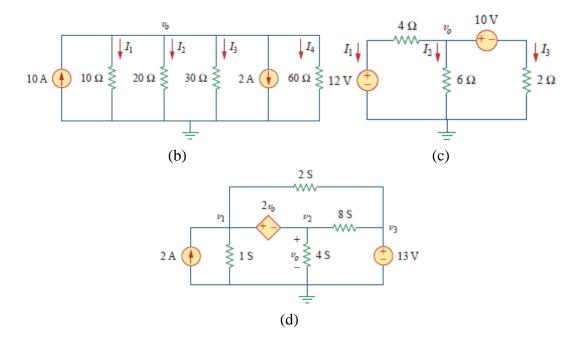

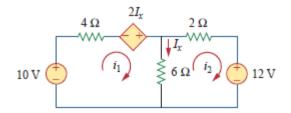

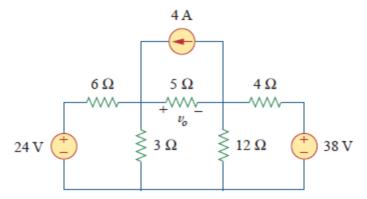

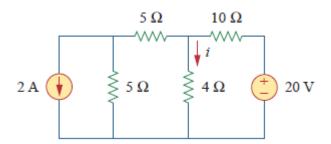

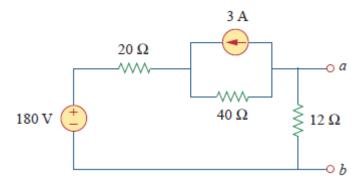

#### 2.10 Sheet 2

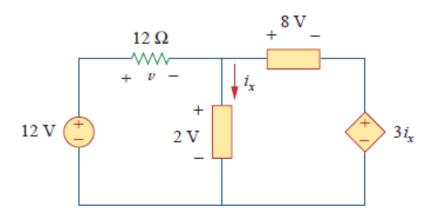

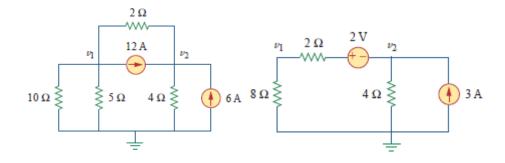

1. Find  $i_1$ ,  $i_2$ , and  $i_3$  in the following figure:

2. Given the circuit in the following figure, use KVL to find the branch voltages  $V_1$  to  $V_4$ .

3. Calculate v and  $i_x$  in the circuit of the following figure:

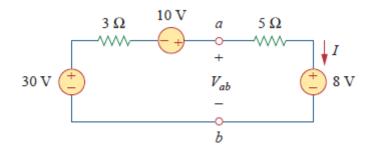

4. Find I and V<sub>ab</sub> in the circuit of the following figure:

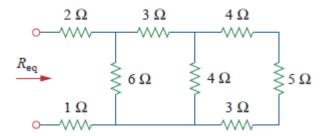

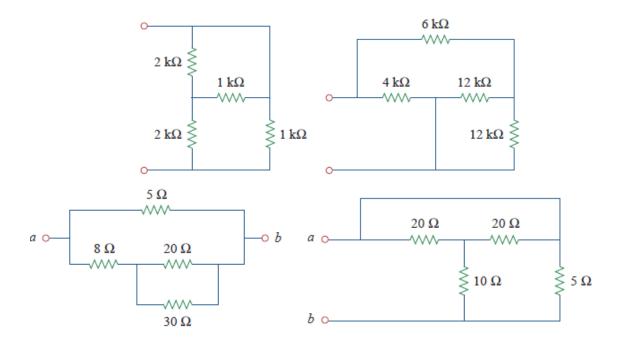

5. Evaluate  $R_{\text{eq}}$  for each of the circuits shown in the following figure:

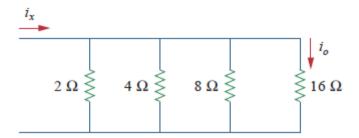

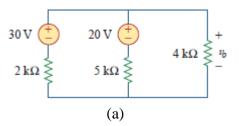

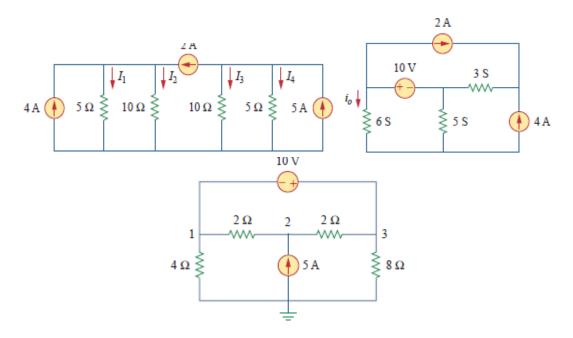

6. Find i<sub>1</sub> through i<sub>4</sub> in the circuit of the following circuit:

7. For the circuit in the following figure,  $i_0$ = 2A. Calculate  $i_x$  and the total power dissipated by the circuit.

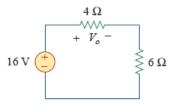

8. Calculate  $V_o$  in the circuit of the following figure:

9. For the circuit in the following figures, obtain  $v_1$  and  $v_2$  by using nodal analysis.

10. For the circuit in the following figures, obtain  $v_0$  by using nodal analysis.

11. For the circuit in the following figures, find all node voltages by using nodal analysis.

- 12. Repeat all the previous problems by using mesh analysis

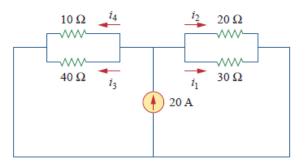

- 13. For the circuit in the following figures, find all currents

14. Determine  $v_0$  in the circuit using the superposition principle.

15. For the circuit, use source transformation to find i.

16. Find the Norton and Thevenin's equivalent with respect to terminals a-b in the circuit shown

## **CHAPTER 3**

# NATURAL AND STEP RESPONSE FOR RL, RC AND RLC CIRCUIT

#### **CHAPTER 3**

## NATURAL AND STEP RESPONSE FOR RL, RC AND RLC CIRCUIT

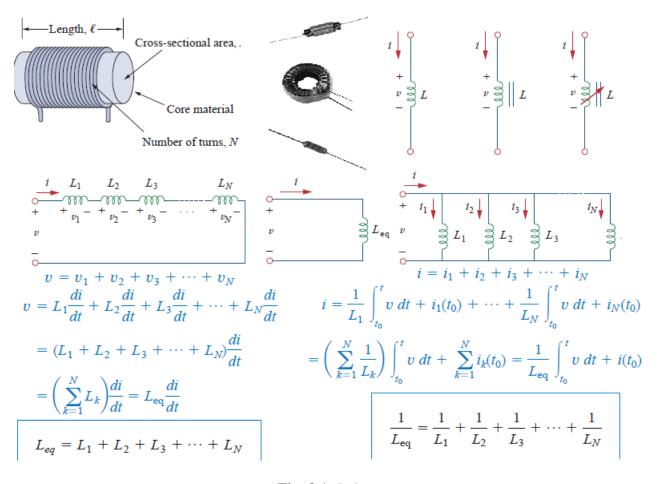

#### 3.1 Inductors

An inductor is a passive element designed to store energy in its magnetic field. Inductors find numerous applications in electronic and power systems. They are used in power supplies, transformers, radios, TVs, radars, and electric motors. Any conductor of electric current has inductive properties and may be regarded as an inductor. But in order to enhance the inductive effect, a practical inductor is usually formed into a cylindrical coil with many turns of conducting wire, as shown in as shown in figure 3.1. An inductor consists of a coil of conducting wire.

Fig. 3.1: Inductors

Inductance is the property whereby an inductor exhibits opposition to the change of current flowing through it, measured in henrys (H).

$$L = N^2 \mu A/l$$

where N is the number of turns, l is the length, A is the cross-sectional area, and  $\mu$  is the permeability of the core

#### 3.2 Capacitors

A capacitor is a passive element designed to store energy in its electric field. Besides resistors, capacitors are the most common electrical components. Capacitors are used extensively in electronics, communications, computers, and power systems.

Fig. 3.2: Capacitors

For example, they are used in the tuning circuits of radio receivers and as dynamic memory elements in computer systems. A capacitor consists of two conducting plates separated by an insulator (or dielectric) as shown in figure 3.2.

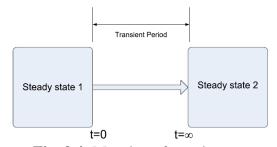

where A is the surface area of each plate, d is the distance between the plates, and E is the permittivity of the dielectric material between the plates. Capacitance is the ratio of the charge on one plate of a capacitor to the voltage difference between the two plates, measured in farads (F). As shown in figure 3.3, we can present a complete comparison between the three passive element.

Important characteristics of the basic elements.†

| Relation                                            | Resistor (R)                             | Capacitor (C)                                 | Inductor $(L)$                                |

|-----------------------------------------------------|------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| v-i:                                                | v = iR                                   | $v = \frac{1}{C} \int_{t_0}^t i  dt + v(t_0)$ | $v = L \frac{di}{dt}$                         |

| i-v:                                                | i = v/R                                  | $i = C \frac{dv}{dt}$                         | $i = \frac{1}{L} \int_{t_0}^t v  dt + i(t_0)$ |

| <i>p</i> or <i>w</i> :                              | $p = i^2 R = \frac{v^2}{R}$              | $w = \frac{1}{2}Cv^2$                         | $w = \frac{1}{2}Li^2$                         |

| Series:                                             | $R_{\rm eq} = R_1 + R_2$                 | $C_{\rm eq} = \frac{C_1 C_2}{C_1 + C_2}$      | $L_{\rm eq} = L_1 + L_2$                      |

| Parallel:                                           | $R_{\rm eq} = \frac{R_1 R_2}{R_1 + R_2}$ | $C_{\rm eq} = C_1 + C_2$                      | $L_{\rm eq} = \frac{L_1 L_2}{L_1 + L_2}$      |

| At dc:                                              | Same                                     | Open circuit                                  | Short circuit                                 |

| Circuit variable<br>that cannot<br>change abruptly: | Not applicable                           | υ                                             | i                                             |

| change abrupity.                                    | rvot applicable                          |                                               | E.                                            |

Fig. 3.3: Comparison between capacitors, inductors and resistors.

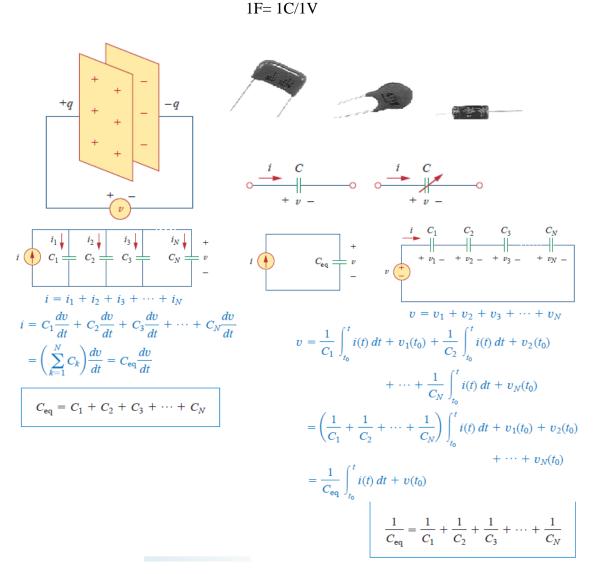

#### 3.3 First order transient circuit

In this chapter, we shall examine two types of simple circuits: a circuit comprising a resistor and capacitor and a circuit comprising a resistor and an inductor. These are called RC and RL circuits, respectively. A first-order circuit is characterized by a first-order differential equation. The meaning of transient is shown in figure 3.4.

Fig. 3.4: Meaning of transient

#### 3.3.1 Source free R-C circuit

A source-free *RC* circuit occurs when its dc source is suddenly disconnected. The energy already stored in the capacitor is released to the resistors (sometimes called free response) as shown in figure 3.5. This shows that the voltage response of the RC circuit is an exponential decay of the initial voltage. Since the response is due to the initial energy stored and the physical characteristics of the circuit and not due to some external voltage or current source, it is called the natural response of the circuit.

Fig. 3.5: Source free R-C circuit

The time constant of a circuit is the time required for the response to decay to a factor of 1/e or 36.8 percent of its initial value. The Key to Working with a Source-free RC Circuit Is Finding:

- $\triangleright$  The initial voltage  $v(0) = V_0$  across the capacitor.

- $\triangleright$  The time constant  $\tau$ .

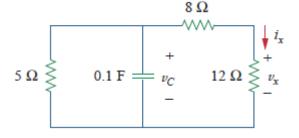

**Example 3.3:** let Vc(0)=15, find  $V_c$ ,  $V_x$  and  $i_x$  for t>0.

Answer: We first need to make the circuit conform with the standard RC circuit.

$$R_{eq} = \frac{20 \times 5}{20 + 5} = 4 \Omega$$

$$\tau = R_{eq}C = 4(0.1) = 0.4 \text{ s}$$

$$v = v(0)e^{-t/\tau} = 15e^{-t/0.4} \text{ V}, \qquad v_C = v = 15e^{-2.5t} \text{ V}$$

$$v_x = \frac{12}{12 + 8}v = 0.6(15e^{-2.5t}) = 9e^{-2.5t} \text{ V}$$

$$i_x = \frac{v_x}{12} = 0.75e^{-2.5t} \text{ A}$$

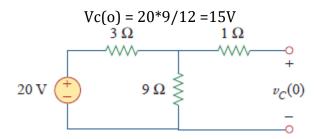

**Example 3.4:** the switch in the circuit in the following Fig. has been closed for a long time, and it is opened at t = 0. Find v(t) for  $t \ge 0$ . Calculate the initial energy stored in the capacitor.

Answer: For t < 0 the switch is closed; the capacitor is an open circuit to dc, as represented in the following figure. Using voltage division

For the switch is opened, and we have the RC circuit shown in the following figure.

9

$$\Omega$$

$\stackrel{\downarrow}{\geqslant}$   $V_o = 15 \text{ V}$   $\stackrel{\downarrow}{=}$  20 mF

[Notice that the RC circuit is source free] The resistors in series give

$$R_{eq} = 9 + 1 = 10$$

The time constant is

$$\tau = R_{eq} * C = 0.2s$$

Thus, the voltage across the capacitor for is

$$v(t) = 15e^{-5t}V$$

The initial energy stored in the capacitor is

$$Wc(0)=0.5 C*V^2=2.25 J$$

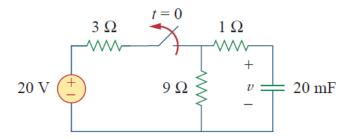

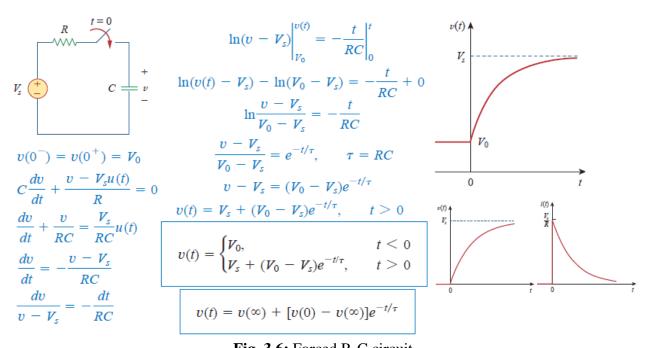

#### 3.3.2 Forced R-C circuit

The steady-state response is the behavior of the circuit a long time after an external excitation is applied. The forced R-C circuit is shown in figure 3.6. with  $v(\infty)$  is the final value of capacitor voltage.

Fig. 3.6: Forced R-C circuit

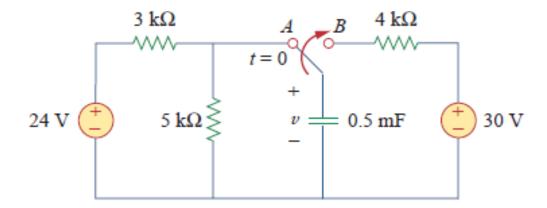

**Example 3.5:** the switch in the following Fig. has been in position A for a long time, and it is moved to B at t = 0. Determine v(t) for t > 0. Calculate its value at t = 1s and t = 4s.

Answer: For t < 0 the switch is at position A. The capacitor acts like an open circuit to dc, but v is the same as the voltage across the resistor 5k. Hence, the voltage across the capacitor just before t=0 is obtained by voltage division as Using the fact that the capacitor voltage cannot change instantaneously,

$$v(0) = \frac{5}{5+3}24 = 15$$

For t>0, the switch is in position B. The Thevenin resistance connected to the capacitor is  $R_{Th} = 4 k$  and the time constant is

$$\tau = R_{eq} * C = 2s$$

Since the capacitor acts like an open circuit to dc at steady state,  $v(\infty) = 30 \text{ V}$

$$v(t) = 30 - 15e^{-0.5t}V$$

at t=1 v=20.9 V

at t=4 v=27.97V

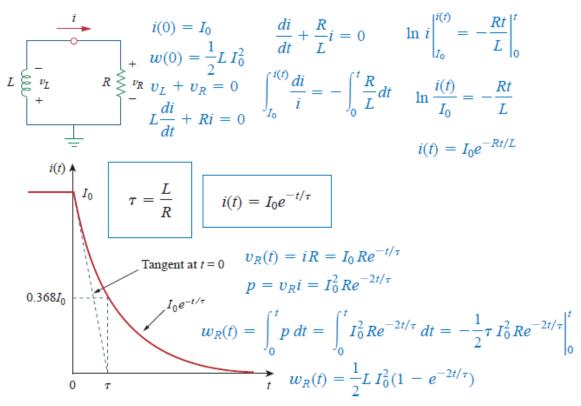

#### 3.3.3 Source free R-L circuit

Consider the series connection of a resistor and an inductor, as shown in Fig. 3.7. Our goal is to determine the circuit response.

Fig. 3.7: Source free R-L circuit

The Key to Working with a Source-free RL Circuit Is Finding:

- $\triangleright$  The initial current  $i(0) = I_0$  through the inductor.

- $\triangleright$  The time constant  $\tau$ .

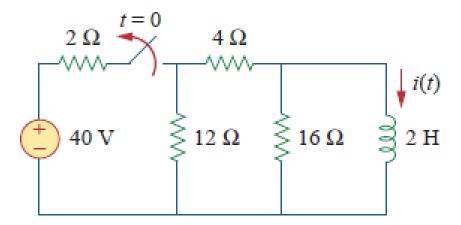

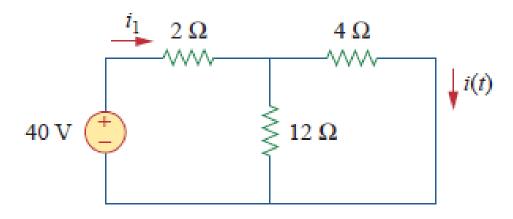

**Example 3.6:** the switch in the circuit in the following Fig. has been closed for a long time, and it is opened at t = 0. Find i(t) for  $t \ge 0$

Answer: When t < 0, the switch is closed, and the inductor acts as a short circuit to dc. The resistor 16 is short-circuited; the resulting circuit is shown. To get  $i_1$  in circuit, we combine the and resistors in parallel.

$$i_1 = \frac{40}{2 + \frac{4 * 12}{12 + 4}} = 8A$$

We obtain i(0) from  $i_1$  using current division, by writing

$$i(t) = \frac{12}{12+4}i_1 = 6A$$

When t > 0, the switch is open and the voltage source is disconnected. We now have the source-free RL circuit. Combining the resistors, we have

$$R_{eq} = (12 + 4)//16 = 8\Omega$$

The time constant is

$$\tau = \frac{L}{R_{eq}} = 0.25 \, s$$

Thus,

$$i(t) = 6e^{-4t}A$$

#### 3.3.4 Forced R-L circuit

The steady-state response is the behavior of the circuit a long time after an external excitation is applied. The forced R-L circuit is shown in figure 3.8. with  $i(\infty)$  is the final value of inductor current.

Fig. 3.8: Forced R-L circuit

**Example 3.7:** Find i(t) in the circuit in the following Fig. for t >0. Assume that the switch has been closed for a long time.

Answer: When t < 0 the 3 ohm resistor is short-circuited, and the inductor acts like a short circuit. The current through the inductor is

$$i(0) = \frac{10}{2} = 5A$$

When t > 0 the switch is open.

$$i(\infty) = \frac{10}{2+3} = 2A$$

The Thevenin resistance across the inductor terminals is

$$R_{Th} = 2 + 3 = 5$$

Thus,

$$i(t) = 2 + 3e^{-15t}A$$

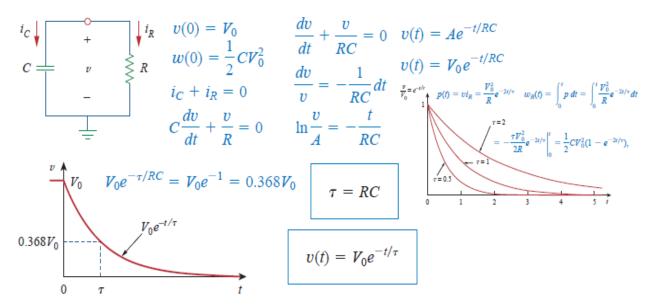

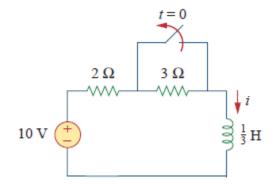

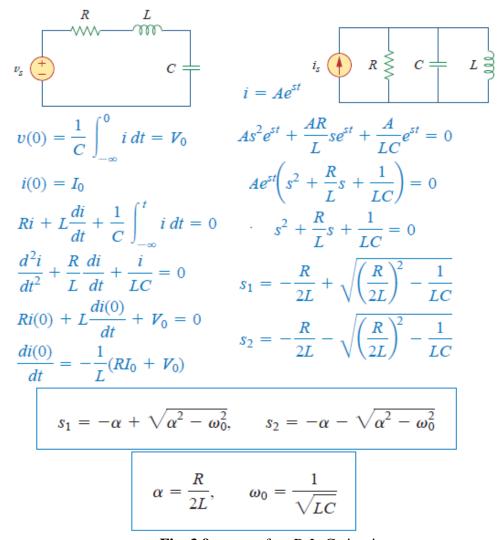

#### 3.4 Second order transient circuit

In this chapter we considered circuits with a single storage element (a capacitor or an inductor). Such circuits are first-order because the differential equations describing them are first-order. In this chapter we will consider circuits containing two storage elements. These are known as *second-order* circuits because their responses are described by differential equations that contain second derivatives. Typical examples of second-order circuits are *RLC* circuits, in which the three kinds of passive elements are present. Examples of such circuits are shown in figure 3.9. A second-order circuit is characterized by a second-order differential equation. It consists of resistors and the equivalent of two energy storage elements.

Fig. 3.9: source free R-L-C circuit

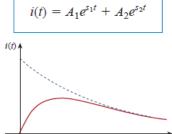

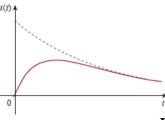

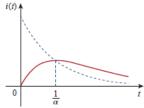

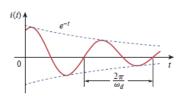

There are three types of solutions as shown in figure 3.10:

- $\triangleright$  If  $\alpha > w_0$  we have the over-damped case.

- $\triangleright$  If  $\alpha = w_0$  we have the critically damped case.

- $\triangleright$  If  $\alpha < w_0$  we have the under-damped case.

### Overdamped Case ( $lpha>\omega_0$ ) Critically Damped Case ( $lpha=\omega_0$ ) Underdamped Case ( $lpha<\omega_0$ )

$$i(t) = (A_2 + A_1 t)e^{-\alpha t}$$

Fig. 3.10: three types of RLC circuit cases.

#### if we have step response

$$v(t) = V_s + A_1 e^{s_1 t} + A_2 e^{s_2 t}$$

(Overdamped)

$v(t) = V_s + (A_1 + A_2 t) e^{-\alpha t}$  (Critically damped)

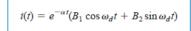

$v(t) = V_s + (A_1 \cos \omega_d t + A_2 \sin \omega_d t) e^{-\alpha t}$  (Underdamped)

**Example 3.8:** In the following figure R = 40 ohm, L = 4 H and C = 0.25 F. Calculate the characteristics roots of the circuit. Is the natural response over damped, under damped and critical damped?

$$\begin{array}{c|c}

R & L \\

\hline

I_o & \\

V_o & \\

\hline

- & C

\end{array}$$

Answer:

$$\alpha = R/2L = 5$$

and  $w_0 = \frac{1}{\sqrt{LC}} = 1$

$\alpha > w_0$  the circuit is over-damped  $S_1 = -0.101$  and  $S_2 = -9.899$

#### 3.5 Sheet 3

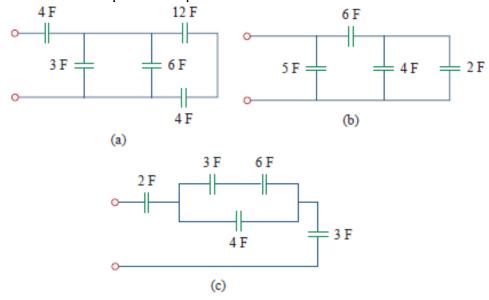

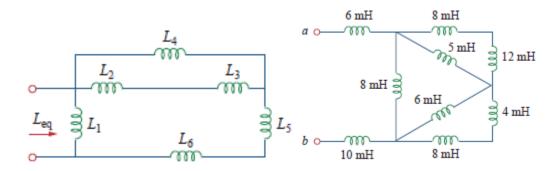

1. Determine the equivalent capacitance for each of the circuits

2. Determine the equivalent inductors for each of the circuits

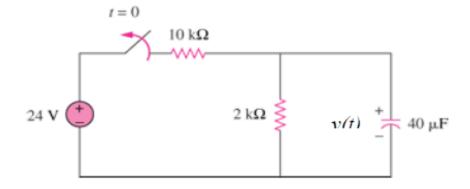

3. The switch in the following figure has been closed for a long time, and it opens at t=0. Find v(t) for t>0.

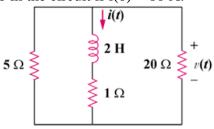

4. Find i(t) and v(t) for t > 0 in the circuit if i(0) = 10 A.

5. Find the capacitor voltage for t < 0 and t > 0 for the circuit

6. Obtain the inductor current for both t < 0 and t > 0 in each of the circuit

- 7. If  $R = 20 \Omega$ , L = 0.6 H, what value of C will make an RLC series circuit:

- (a) Over-damped.

- (b) critically damped.

- (c) under-damped.

- 8. Find v(t) for t > 0 if v(0) = 6 V and i(0) = 2 A in the circuit

## **CHAPTER 4**

## SINUSOIDAL STEADY STATE ANALYSIS

#### **CHAPTER 4**

#### SINUSOIDAL STEADY STATE ANALYSIS

#### 4.1 Phasors and sin wave

Thus far our analysis has been limited for the most part to dc circuits: those circuits excited by constant or time-invariant sources. We have restricted the forcing function to dc sources for the sake of simplicity, for pedagogic reasons, and also for historic reasons. Historically, dc sources were the main means of providing electric power up until the late 1800s. At the end of that century, the battle of direct current versus alternating current began. Both had their advocates among the electrical engineers of the time. Because ac is more efficient and economical to transmit over long distances, ac systems ended up the winner. Thus, it is in keeping with the historical sequence of events that we considered dc sources first. We now begin the analysis of circuits in which the source voltage or current is time-varying. In this chapter, we are particularly interested in sinusoidal time-varying excitation, or simply, excitation by a *sinusoid*. A sinusoid is a signal that has the form of the sine or cosine function as shown in figure 4.1.

Fig. 4.1: Sinusoidal wave properties

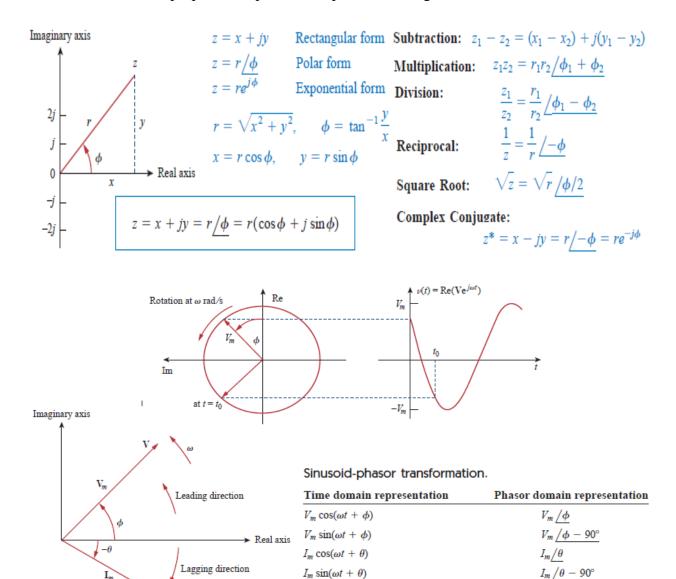

A phasor is a complex number that represents the amplitude and phase of a sinusoid. The properties of phasors are presented in figure 4.2.

Fig. 4.2: phasor properties

#### 4.2 Electrical circuit analysis

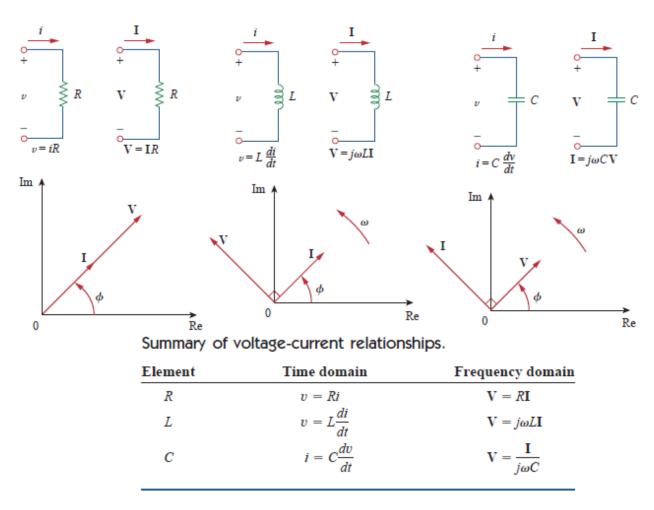

Phasor relationships of circuit elements are summarized in figure 4.3

Fig. 4.3: Phasor relationships of circuit elements

Now we can solve any problem from chapter 2 contains R, L and C, if we have its impedance not resistance only that is meaning real and imaginary ( we can use nodal and mesh analysis, source transform, superposition, thevenin and norton ) for example in figure 4.4.

#### 4.3 Average and RMS

The two important parameter in electronics calculations is average and root mean square value which are discussed here.

$$v_{avg} = \frac{1}{T} \int_0^T v(t) dt$$

Given a periodic function, its rms value (or the effective value) is given by

$$v_{rms} = \sqrt{\frac{1}{T}} \int_{0}^{T} v^{2}(t) dt$$

$$v_{1} = \int_{0}^{10} \frac{\Omega}{v_{2}} \qquad v_{2} \qquad v_{3} \Omega \qquad v_{2} \qquad v_{3} \Omega \qquad v_{4} \Omega \qquad v_{5} \Omega \qquad v_{5} \Omega \qquad v_{7} \Omega \qquad$$

For mesh 2,  $(5+j3-j6)\mathbf{I}_2 - (2+j)\mathbf{I}_1 = 0$ At node 2,  $0 = -(2 + j)\mathbf{I}_1 + (5 - j3)\mathbf{I}_2$  $\frac{V_1 - V_2}{10} + \frac{V_1 - V_2}{-i5} + 1 + j = \frac{V_2}{i10}$  $10(1+j) = -(1+j2)V_1 + (1+j)V_2$  $V_2 = 27.87 \angle 140.6^{\circ} V$

🧃 j2 Ω

Fig. 4.4: Example on circuit analysis with R, L and C

I1-I2

-I2

#### **4.4** Sheet 4

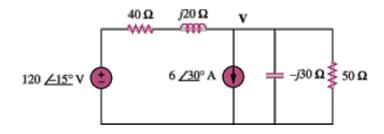

1.Use nodal analysis to find V in the circuit

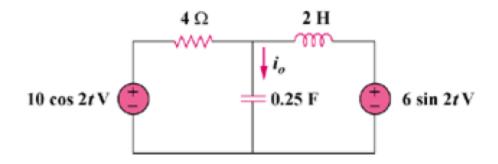

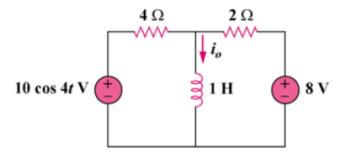

2. Solve for i<sub>0</sub> in the following figure using mesh analysis.

3. Determine  $v_0$  in the circuit in the following figure

4. Find i<sub>0</sub> in the circuit shown by using superposition.

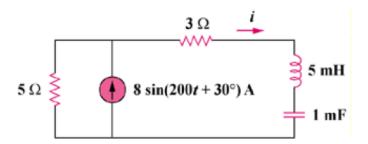

5. Using source transformation, find i in the circuit

## **CHAPTER 5**

## INTRODUCTION OF SEMICONDUCTORS

# **CHAPTER 5**

# INTRODUCTION OF SEMICONDUCTORS

#### **5.1** Fundamentals of atoms

#### 5.1.1 Definitions of atom:

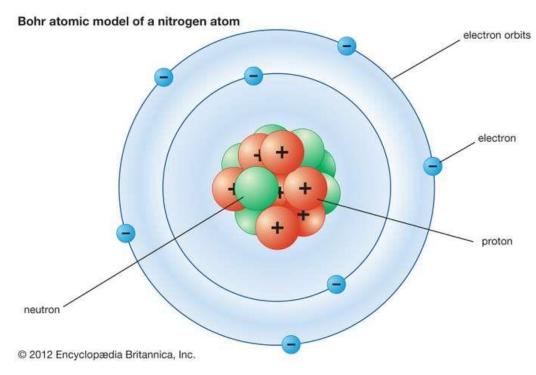

The atom is considered the smallest particle of the element. In addition to it is retaining the characteristics of matter such as if the atom was conductor for example, the matter of it must be conductor too. Finally, we can say that any atom has unique description. As shown in Fig. 5.1, Bohr model was describing the atomic structure

Fig. 5.1: Bohr model for atomic structure

# 5.1.2 Atomic number and Atomic weight

We can describe the atomic number by number of electrons or number of protons at the neutral state. In addition to describe atomic weight by number of electrons or number of protons plus number neutrons at the neutral state

#### 5.1.3 Orbits and shells

The electrons orbits around the nucleus. Each electron orbits in the specified orbit. Each orbit has fixed energy level. The energy of orbit is increasing with increasing the radius of the orbit. Some of orbits complete shell. In contrast that, we have big difference between orbit and shell. In the view of shell, each atom has fixed number of shell. Each shell has maximum number of electrons. The energy gap between two shell is larger than energy gap between two orbits at the same shell.

#### **5.2** Basic of materials

To classify the materials according to their conductivity we must first define the main parameter in material which is called resistivity.

# 5.2.1 Resistivity

We can define the resistivity as resistance of matter against flow the electrical current. Now the differences between materials will be stated in the following subsection.

## 5.2.2 Insulators, semiconductors and conductors

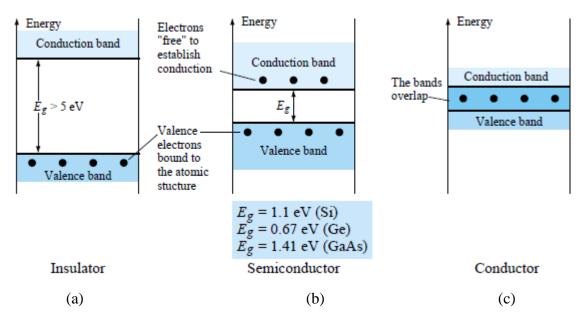

As shown in Fig. 5.2, The material will be classified into three type according to its resistivity by energy diagram as the following:

- ➤ Insulators: this type contain wide energy gap between valence band and conduction band. Its conduction band hasn't any of free electrons. Its valence band contains very few valence electrons. The valence electron needs high work function to transfer from valance band to conduction band.

- Semiconductors: this type contain energy gap between valence band and conduction band but narrow than in insulators. Its conduction band has few number of free electrons. Its valence band contains few valence electrons. The valence electron needs moderate work function to transfer from valance band to conduction band.

- ➤ Conductors: this type contain overlapping between valence band and conduction band. The free electrons is exist already in conduction band. Its valence band contains high numbers of

valence electrons. The valence electron needs small work function to transfer from valance band to conduction band.

Fig. 5.2: Energy diagram for (a)Insulators, (b)Semiconductors and (c)conductors

# **5.3** Semiconductor concepts

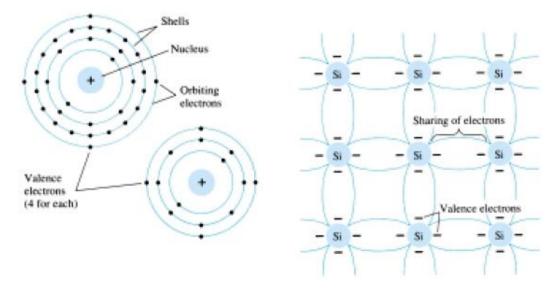

As shown in Fig. 5.3, the intrinsic semiconductor is obtained. The more popular semi conductor materials are Silicon (Si) which has 14 electrons and germanium (Ge) which has 32 electrons. All semiconductors have 4 electrons at the Fermi level.

Fig. 5.3: Intrinsic semiconductor.

## 5.3.1 Doping process

The doping is control process by adding impurities to pure semiconductors to enhance its conductivity to electrical current.

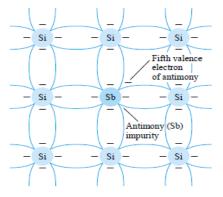

#### 5.3.2 N-type material

This type is negative type with majority of electrons and minority of holes. The doping in this type is happened by pentavalent atom which has five electrons in the Fermi level. Four of them complete covalent bonds and still one free electron to conduct electrical current as shown in Fig. 5.4.

Fig. 5.4: N-type material.

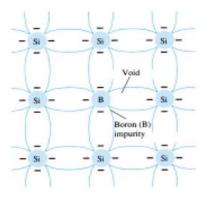

# 5.3.3 P-type material

This type is positive type with majority of holes and minority of electrons. The doping in this type is happened by trivalent atom which has three electrons in the Fermi level. all of them complete covalent bonds and still one hole need one free electron to conduct electrical current as shown in Fig. 5.5.

Fig. 5.5: P-type material.

# 5.3.4 Depletion layer

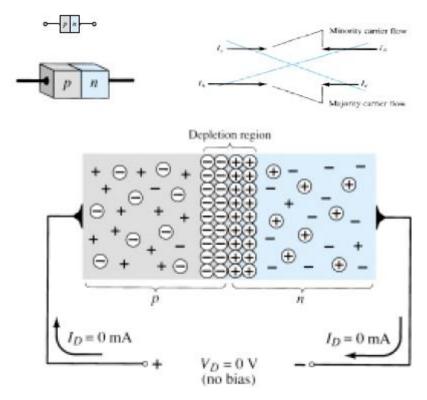

First, we will put N-type material beside P-type material. The diffusion of electrons will be happened from N-type to P-type. The second step is the recombination between electrons and holes to complete electron and hole pairs. The third step is the ionization which makes the N-type change from neutral state to positive ions (Donors atoms) and the P-type change from neutral state to negative ions (Acceptors atoms). At the equilibrium between the attraction force between positive ions and electrons and the repulsion force between negative ions and electrons complete the depletion layer as shown in Fig. 5.6.

Fig. 5.6: PN junction.

# 5.3.5 Barrier potential

This potential represent the depletion layer or depletion region and it is equal to 0.7 in Si and 0.3 in Ge.

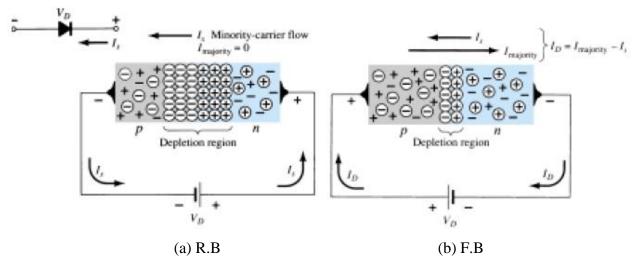

#### 5.3.6 Forward bias and reverse bias

As shown in Fig. 5.7, the biasing in the PN junction which is called diode is classified into two types as the following:

Forward bias (F.B): the connection is positive DC battery with P-type and negative DC battery with N-type generate two repulsion force between them then depletion region width is reduced then flow the electrical current  $I_D$ .

$$I_D = I_S(e^{\frac{kV_d}{T_k}} - 1) (5-1)$$

where:

$V_d$ : Voltage on diode.

k: 11,600/ $\eta$  with  $\eta$  = 1 for Ge and  $\eta$  = 2 for Si.

$$T_k$$

:  $T_C + 273$ .

Reverse bias (R.B): the connection is positive DC battery with N-type and negative DC battery with P-type generate two attraction force between them then depletion region width is increased then no flow the electrical current or flow small reverse saturation current  $I_s$ .

Fig. 5.7: Diode biasing.

#### 5.3.7 Electronic and hole currents

The electron current generates the electrical current at the against direction. In addition to, the hole current generates the electrical current at the same direction.

# **5.4** Sheet 5

- 1. Define an Atom?

- 2. What is the difference between atomic number and mass number?

- 3. What is the difference between orbit and shell?

- 4. Define the resistivity?

- 5. What are the differences between conductor, insulators and semiconductor?

- 6. Define doping process?

- 7. How N-type is created?

- 8. How P-type is created?

- 9. How Depletion layer (region) is created, then define the barrier potential?

- 10. What are the differences between forward and reverse biasing?

- 11. What is the difference between electron and hole currents?

# CHAPTER 6 DIODE AND ITS APPLICATIONS

# **CHAPTER 6**

# **DIODE AND ITS APPLICATIONS**

#### **6.1** Introduction of diode

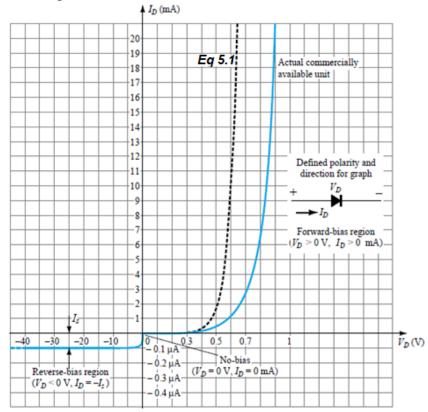

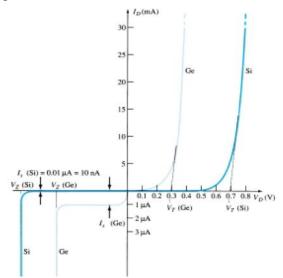

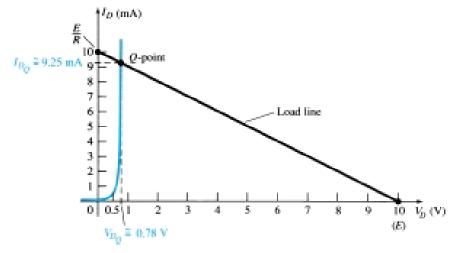

We can show the characteristics curve for diode can be presented as shown in Fig. 6.1 but first we will present all models diode to arrive it.

**Fig. 6.1:** Characteristics curve for Si diode.

#### 6.2 models of diode

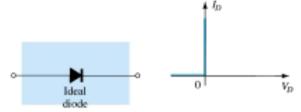

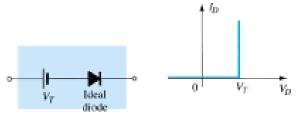

#### 6.2.1 ideal model

As shown in Fig. 6.2, this model make diode as short circuit when is connected as F.B and open circuit when connected at R.B.

Fig. 6.2: Ideal model.

#### **6.2.2** Barrier constant model

As shown in Fig. 6.3, this model make diode as Battery when is connected as F.B and open circuit when connected at R.B.

Fig. 6.3: Barrier potential (constant) model.

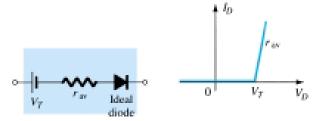

#### 6.2.3 Linear model

As shown in Fig. 6.4, this model make diode as battery with resistor when is connected as F.B and open circuit when connected at R.B.

Fig. 6.4: Linear (piecewise) model.

#### 6.2.4 Actual model

As shown in Fig. 6.5, this model make diode as battery with resistor when is connected as F.B and high resistor when connected at R.B.

Fig. 6.5: Actual (Practical) model.

# 6.3 Applications of diode

# 6.3.1 DC applications of diode

We use the section 6.2 to solve any problem here such as the following example:

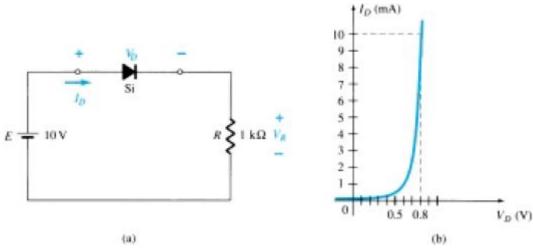

**Example 6.1:** For the series diode configuration of Fig. 6.6 (a) employing the diode characteristics of Fig. 6.6 (b) determine:

- a)  $V_{dQ}$  and  $I_{dQ}$ .

- b)  $V_R$ .

**Fig. 6.6:** Example 6.1.

#### **Solution:**

By graph

$$I_D(at V_D = 0) = \frac{E}{R} = 5 mA$$

$V_D(at I_D = 0) = E = 10 V$

draw load line

$V_{dQ} = 0.78 V$  and  $I_{dQ} = 9.25 mA$ .

$$V_R = E - V_{dQ} = 9.22 \text{ V or}$$

$V_R = R * I_{dO} = 9.25 \text{ V}$

without graph

Diode (F.B)

Assume constant model:  $V_{dQ} = 0.7$ V and  $I_{dQ} = 10-0.7/1$  K= 9.3 mA.

$$V_R = E - V_{dQ} = R * I_{dQ} = 9.3 \text{ V}$$

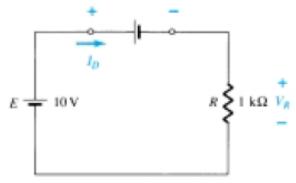

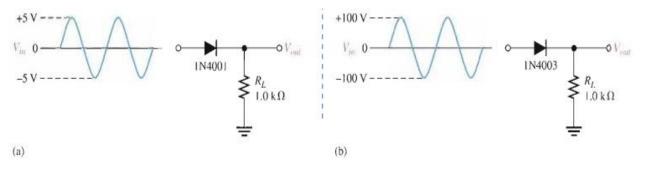

# 6.3.2 AC applications of diode

We will present two main application in this subsection such as the following:

➤ Half wave rectifier (HWR):

Here we put time analysis in our vision as shown in Fig. 6.7 (a). The input sinusoidal wave enter to diode to half of it pass and diode prevent another half. To know how we do that, we will analyze the circuit:

- 1. Assume ideal model.

- 2. At positive half cycle:

Diode (F.B).

$$V_{o} = V_{i}$$

.

output signal is shown in Fig. 6.7 (b).

3. At negative half cycle:

Diode (F.B).

$$V_0 = 0 \text{ V}.$$

output signal is shown in Fig. 6.7 (c).

- 4. The effect of barrier potential on HWR is shown in Fig. 6.7 (d).

- 5. The average voltage equal to  $V_{DC} = V_{avg} = \frac{V_m}{\pi}$  as shown in Fig. 6.7 (e).

- 6. Peak inverse voltage PIV =  $V_K V_A$  (when Diode of f) =  $V_m$ .

Fig. 6.7: HWR circuit.

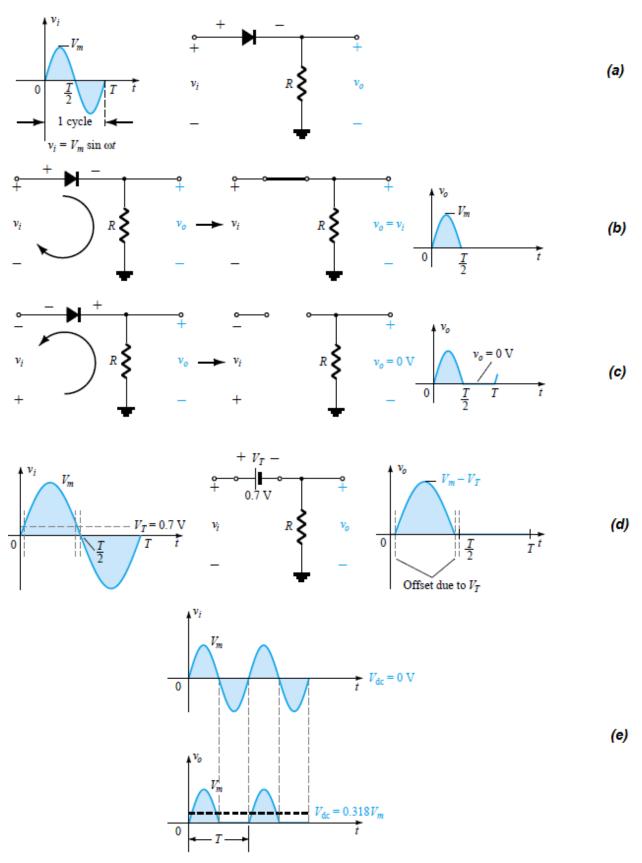

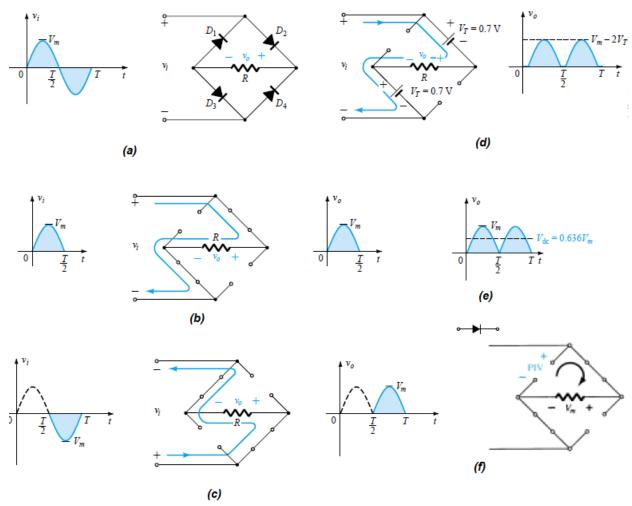

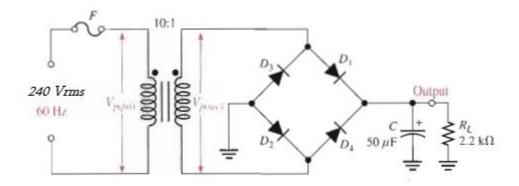

#### > Full wave rectifier (FWR):

Here we put time analysis in our vision as shown in Fig. 6.8 (a) and Fig. 6.9 (a). The input sinusoidal wave enter to diode to half of it pass as it is and diode reverse another half from negative to positive such as example. We can classify the full wave rectifier to two types:

#### **Center-Tapped transformer FWR**

To know how we do that, we will analyze the circuit:

- 1. Assume ideal model and

- 2. (V at secondary = V at primary \* Number of secondary turns/ number of primary turns).

- 3. At positive half cycle:

$$V_{o} = V_{i}$$

.

output signal is shown in Fig. 6.8 (b).

4. At negative half cycle:

$$V_{o} = V_{i}$$

.

output signal is shown in Fig. 6.8 (c).

- 5. The average voltage equal to  $V_{DC} = V_{avg} = \frac{2*V_m}{\pi}$ .

- 6. Peak inverse voltage

PIV =

$$V_K - V_A$$

(when Diode of f) =  $2V_m$  as shown in Fig. 6.8 (d).

7. The effect of barrier potential on FWR.

$$V_o = V_i - V_T (V_T = V_B).$$

$$V_{DC} = V_{avg} = \frac{2 * (V_m - V_T)}{\pi}$$

$$PIV = V_K - V_A(when\ Diode\ off) = 2V_m - V_T$$

8. No turns ratio effect on FWR and barrier potential model.

$$V_o = (V_i/2) - V_T (V_T = V_B).$$

$$V_{DC} = V_{avg} = \frac{2 * ((V_m/2) - V_T)}{\pi}$$

$$PIV = V_K - V_A(when\ Diode\ off) = V_m - V_T$$

Fig. 6.8: Center-tapped circuit.

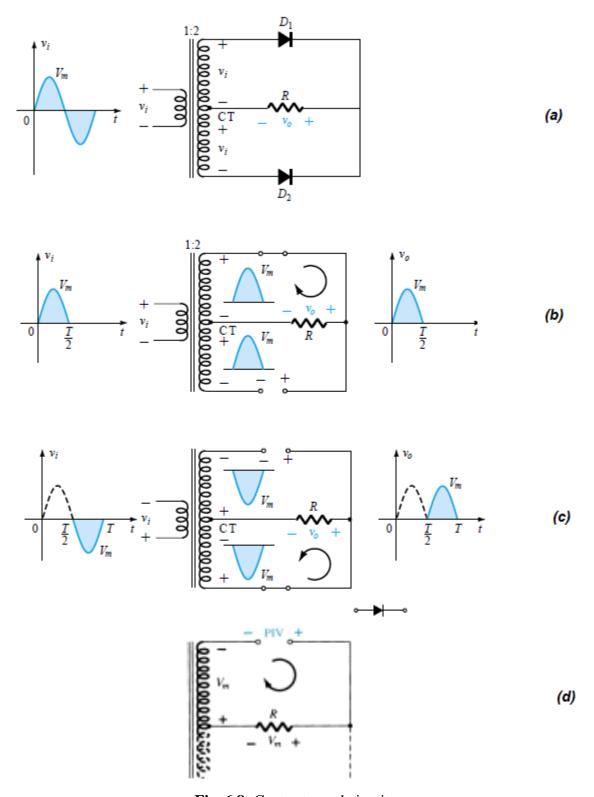

#### **Bridge FWR**

To know how we do that, we will analyze the circuit:

- 1. Assume ideal model.

- 2. At positive half cycle: D2, D3 (F.B) and D1, D4(R.B).  $V_o = V_i$ . output signal is shown in Fig. 6.9 (b).

- 3. At negative half cycle: D2, D3 (R.B) and D1, D4(F.B).  $V_0 = V_i$ . output signal is shown in Fig. 6.9 (c).

- 4. The average voltage equal to  $V_{DC} = V_{avg} = \frac{V_m}{\pi}$  as shown in Fig. 6.9 (e).

- 5. PIV =  $V_K V_A$  (when Diode of f) =  $V_m$  as shown in Fig. 6.9 (f).

- 6. The effect of barrier potential on FWR as shown in Fig. 6.9 (d).

$$V_o = V_i - 2V_T (V_T = V_B).$$

$$V_{DC} = V_{avg} = \frac{2 * (V_m - 2V_T)}{\pi}$$

$PIV = V_K - V_A(when \ Diode \ of f) = V_m - V_T$

Fig. 6.9: Bridge circuit.

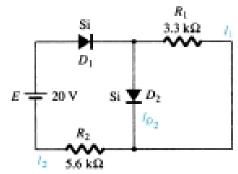

# **6.4** Sheet 6

- 1. Describe the models of diode?

- 2. What is the difference between half wave rectifier and full wave rectifier in terms of PIV and average voltage?

- 3. Determine the currents of diodes in the following figure?

4. Draw the output voltages of each rectifier for the following figures?

5. Determine the output voltage and draw its waveform for the following figure, then calculate PIV and Vdc?

# **Chapter 7**

**Different Types of Transistors**

# **Chapter 7**

# **Different Types of Transistors**

# 7.1 Introduction of Bipolar Junction Transistor (BJT)

During the period 1904–1947, the vacuum tube was undoubtedly the electronic device of interest and development. In 1904, the vacuum-tube diode was introduced by J. A. Fleming. Shortly thereafter, in 1906, Lee De Forest added a third element, called the control grid, to the vacuum diode, resulting in the first amplifier, the triode. In the following years, radio and television provided great stimulation to the tube industry. Production rose from about 1 million tubes in 1922 to about 100 million in 1937. In the early 1930s the four-element tetrode and five-element pentode gained prominence in the electron-tube industry. In the years to follow, the industry became one of primary importance and rapid advances were made in design, manufacturing techniques, high-power and high-frequency applications, and miniaturization.